hitArbiter sign -off and design flow

550 likes | 698 Views

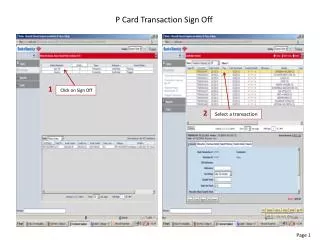

This document outlines the design, verification, and sign-off process for the Hit Arbiter system developed by A. Kluge. It details block diagrams, the structure of the hit arbiter and controller, simulation results, limitations, and timings, including clock synchronization at 320 MHz. The system addresses issues related to hit processing and pile-up, providing metrics for error probability and timing delays and confirming that necessary design constraints are met during the synthesis and place-and-route phases. Key achievements include automatic verification of hits and addressing for high-rate hit generation.

hitArbiter sign -off and design flow

E N D

Presentation Transcript

hitArbiter sign-off and design flow A. Kluge Jan 18, 2013

TDCpix block diagram A. Kluge

pixel groups A. Kluge

hitArbiter(daq_rdy = ‘1’) in0 in1 in2 in3 in4 clk_sync daq_rdy hit lead_edge trail_edge parallel_load_i_out pileup<4:0>: “01110” address<4:0>: “00001” A. Kluge

hitArbiter(daq_rdy = ‘01’) in0 in1 in2 in3 in4 clk_sync daq_rdy hit lead_edge trail_edge parallel_load_i_out pileup<4:0>: “11110” address<4:0>: “00001” A. Kluge

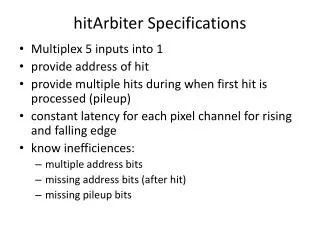

hitArbiter • Implementation divided into • hitArbiter & • hitArbiterController A. Kluge

hitArbiter A. Kluge

hitArbiterController A. Kluge

hitArbiterController A. Kluge

hitArbiter limitations • If a hit arrives while another is still active • it cannot be processed • hitArbiter blocks it out • hitArbiter sets the corresponding pile-up bit • If two or more hits arrive at almost the time • more than one hit will be flagged in the address bus • probability < 2 * 10-4 • Timing is correct for one of them unknown which • Pile-up control signal needs to travel from hitArbiterControllerback to the pile-up flip flops. • pile-up might be missed • probability < 7* 10-4 A. Kluge

Design • hitArbiternetlist written by hand • hitArbiterController synthesized • Automatically placed & routed A. Kluge

Design & Verification • Gate level netlist & sdfbackannotation simulated @ clk_sync = 320 MHz • hitGenerator used as stimulus • hitGenerator sends hits: • for highest rate center column: • 3.3 MHz/column • 144 kHz for center pixel • corresponds to 1 Ghz particle rate instead of 750 MHz / + 33% • according to front-end transfer function of TDCpix demonstrator for a threshold of 0.7 fC • hitArbiter8 = pixel group with center pixel A. Kluge

Design & Verification • full automatic verification (no wave views) of: • correct hit address or pile-up address • correct timing of lead_trigger/trail_trigger signal • constant propagation delay for each channel • # hits lost • # pile-up • # double addresses A. Kluge

Simulation results all channels have constant latency A. Kluge

Qchip sign-off and design flow Syn 2013 01 22 Pnr 2013 01 22

Demonstrator: Known bugs • HitArbiter • When same pixel in a group is hit twice consecutively, absolute delay is shorter but constant • Can be corrected off-line • Problem identified and corrected • After pileup, pileup address is reset only after the next hit in the group (if pileup TOT signal goes low after first hit) • Can be corrected off-line • some smaller effect problems identified and corrected using • Detailed VHDL simulation

signoff • run backannotated simulation • clk_sync = 320 • slowProc/typProc/fastProc : • 20130122 / - / 20130122 • verify sdf.log file; check date and warning free: • 20130122 /-/20130122 • For min, negative delays in interconnect are set to 0. • SEU maxf-fastProc: • x

signoff • verify synthesis constraints, 20130122 • sdc/constraints.sdc • verify timing libraries used for syn & pnr • 20130122 • init.tcl in syn/script • set ec::LIBRARY "$IBM_PDK/ibm_cmos8rf/std_cell/rel$PDK_OPT/synopsys_1.2/slow_v110_t125/IBM_CMOS8RF_STD_SLOW_V110_T125.lib \ $IBM_PDK/ibm_cmos8rf/short_io/rel$PDK_OPT/synopsys/slow_v108_t125_pv162/IBM_CMOS8RF_BASE_SHORT_IO_SLOW_V108_T125_PV162.lib " • oa.conf in pnr/script • set rda_Input(ui_timelib,max) { ./synopsys_std_cell_1.2/slow_v110_t125/IBM_CMOS8RF_STD_SLOW_V110_T125.lib \./synopsys_short_io/slow_v108_t125_pv162/IBM_CMOS8RF_BASE_SHORT_IO_SLOW_V108_T125_PV162.lib } • set rda_Input(ui_timelib,min) { ./synopsys_std_cell_1.2/fast_v130_tm55/IBM_CMOS8RF_STD_V12_FAST_V130_TM55.lib \./synopsys_short_io/fast_v132_tm40_pv363/IBM_CMOS8RF_BASE_SHORT_IO_FAST_V132_TM40_PV363.lib } • run synthesis, 20130118

signoff • verify triplication survived syn & pnr: • no triplication • verify latest rc.log for errors or not understood warning • 20130122 • run place and route • verify latest encounter.log for errors or not understood warnings • 20130108 • verify power distribution: • power report & rail_analysis: in ../report/powerReports/ • qchip2010_view_max.rpt/qchip2010_view_min.rpt/qchip2010_view_typ.rpt, 20130108 • rail_analysis in encounter.logfile • 20130122

static power report (20120122) • < 0.3 mWfor min/typ/max case • 20130108 • clk sync = 420 MHz • activity = 30%

Timing (20130122) • Constraints: • clk_sync = 420 MHz • Sign off all hold met: • Max_cap: 0 errors • Fan out: o errors • In2reg hold: slack 151ps • Reg2out hold: 112ps slack • in2out: slack 800 ps

signoff-reg2out -> 20130122 • ############################################################### • Path 1: MET Late External Delay Assertion • Endpoint: parallel_load_i_out (v) checked • with leading edge of 'clk_ro_in' • Beginpoint: i_hitArbiterController2010a/parallel_load_requ_reg/QBAR (v) • triggered by leading edge of 'clk_ro_in' • Path Groups: {reg2out} • Other End Arrival Time 0.000 • + Source Insertion Delay -0.030 • - External Delay 1.500 • + Phase Shift 2.380 • = Required Time 0.850 • - Arrival Time 0.744 • = Slack Time 0.106 • Clock Rise Edge 0.000 • + Source Insertion Delay 0.030 • = Beginpoint Arrival Time 0.030 • +----------------------------------------------------------------------------------------------------------------------------+ • | Instance | Arc | Cell | Slew | Delay | Arrival | Required | • | | | | | | Time | Time | • |----------------------------------------------------+-----------------------+----------+-------+-------+---------+----------| • | | clk_ro_in ^ | | 0.000 | | 0.030 | 0.136 | • | clk_ro_in__L1_I0 | A ^ -> Z v | CLKI_Q | 0.050 | 0.164 | 0.194 | 0.300 | • | clk_ro_in__L2_I0 | A v -> Z ^ | INVERT_O | 0.072 | 0.041 | 0.234 | 0.340 | • | i_hitArbiterController2010a/parallel_load_requ_reg | CLK ^ -> QBAR v | DFF_K | 0.070 | 0.373 | 0.607 | 0.713 | • | i_buf_parallel_load_i_out | A v -> Z v | BUFFER_O | 0.126 | 0.132 | 0.739 | 0.845 | • | | parallel_load_i_out v | | 0.126 | 0.005 | 0.744 | 0.850 | • +----------------------------------------------------------------------------------------------------------------------------+ • -----------

signoff-in2reg_hold -> 20130122 • effected signals: reset/daq_rdy • min reset/daq_rdy delay is set to 0.2ns slack is -0.054/0.052ns, effective min delay is 0.254/0.252 ns • ############################################################### • # Generated by: Cadence Encounter 09.12-s159_1 • # OS: Linux x86_64(Host ID lnxmics3) • # Generated on: Tue Jan 22 17:28:06 2013 • # Command: timeDesign -si -signoff -hold -pathReports -slackReports -numPaths 50 -prefix signoff -outDir ../report/timingReports • ############################################################### • Path 1: VIOLATED Hold Check with Pin i_DFF_reset/CLK • Endpoint: i_DFF_reset/D (^) checked with leading edge of 'clk_ro_in' • Beginpoint: reset (^) triggered by leading edge of 'clk_ro_in' • Path Groups: {in2reg} {inclkSrc2reg} • Other End Arrival Time 0.235 • + Hold -0.011 • + Phase Shift 0.000 • = Required Time 0.224 • Arrival Time 0.170 • Slack Time -0.054 • Clock Rise Edge 0.000 • + Input Delay 0.200 • + Source Insertion Delay -0.030 • = Beginpoint Arrival Time 0.170 • Timing Path: • +--------------------------------------------------------------------+ • | Instance | Arc | Cell | Slew | Delay | Arrival | Required | • | | | | | | Time | Time | • |-------------+---------+-------+-------+-------+---------+----------| • | | reset ^ | | 0.000 | | 0.170 | 0.224 | • | i_DFF_reset | D ^ | DFF_K | 0.001 | 0.000 | 0.170 | 0.224 | • +--------------------------------------------------------------------+ • Clock Rise Edge 0.000 • + Source Insertion Delay 0.030 • = Beginpoint Arrival Time 0.030 • Other End Path: • +--------------------------------------------------------------------------------+ • | Instance | Arc | Cell | Slew | Delay | Arrival | Required | • | | | | | | Time | Time | • |------------------+-------------+----------+-------+-------+---------+----------| • | | clk_ro_in ^ | | 0.000 | | 0.030 | -0.024 | • | clk_ro_in__L1_I0 | A ^ -> Z v | CLKI_Q | 0.050 | 0.164 | 0.194 | 0.140 | • | clk_ro_in__L2_I0 | A v -> Z ^ | INVERT_O | 0.072 | 0.041 | 0.234 | 0.181 | • | i_DFF_reset | CLK ^ | DFF_K | 0.072 | 0.000 | 0.235 | 0.181 | • +--------------------------------------------------------------------------------+

signoff reg2reg hold (20130122) • Violation by 28 ps clock uncertainty of 30 ps is taken into account for timing but obviosly not for place&route. • However, clock uncertainty of 30 ps is overestimated for such a samall block • ############################################################### • # Generated by: Cadence Encounter 09.12-s159_1 • # OS: Linux x86_64(Host ID lnxmics3) • # Generated on: Tue Jan 22 17:28:06 2013 • # Command: timeDesign -si -signoff -hold -pathReports -slackReports -numPaths 50 -prefix signoff -outDir ../report/timingReports • ############################################################### • Path 1: VIOLATED Hold Check with Pin i_hitArbiterController2010a/reset_pileup_ • int_reg/CLK • Endpoint: i_hitArbiterController2010a/reset_pileup_int_reg/D (^) checked with • leading edge of 'clk_ro_in' • Beginpoint: i_DFF_reset/Q (v) triggered by • leading edge of 'clk_ro_in' • Path Groups: {reg2reg} • Other End Arrival Time 0.235 • + Hold -0.012 • + Phase Shift 0.000 • = Required Time 0.222 • Arrival Time 0.195 • Slack Time -0.028 • Clock Rise Edge 0.000 • + Source Insertion Delay -0.030 • = Beginpoint Arrival Time -0.030 • Timing Path: • +-----------------------------------------------------------------------------------------------------------------+ • | Instance | Arc | Cell | Slew | Delay | Arrival | Required | • | | | | | | Time | Time | • |--------------------------------------------------+--------------+----------+-------+-------+---------+----------| • | | clk_ro_in ^ | | 0.000 | | -0.030 | -0.002 | • | clk_ro_in__L1_I0 | A ^ -> Z v | CLKI_Q | 0.017 | 0.067 | 0.037 | 0.064 | • | clk_ro_in__L2_I0 | A v -> Z ^ | INVERT_O | 0.022 | 0.018 | 0.054 | 0.082 | • | i_DFF_reset | CLK ^ -> Q v | DFF_K | 0.037 | 0.098 | 0.153 | 0.180 | • | i_hitArbiterController2010a/p0003A | A v -> Z ^ | NOR2_B | 0.061 | 0.042 | 0.195 | 0.222 | • | i_hitArbiterController2010a/reset_pileup_int_reg | D ^ | DFF_K | 0.061 | 0.000 | 0.195 | 0.222 | • +-----------------------------------------------------------------------------------------------------------------+ • Clock Rise Edge 0.000 • + Source Insertion Delay 0.030 • = Beginpoint Arrival Time 0.030 • Other End Path: • +----------------------------------------------------------------------------------------------------------------+ • | Instance | Arc | Cell | Slew | Delay | Arrival | Required | • | | | | | | Time | Time | • |--------------------------------------------------+-------------+----------+-------+-------+---------+----------| • | | clk_ro_in ^ | | 0.000 | | 0.030 | 0.002 | • | clk_ro_in__L1_I0 | A ^ -> Z v | CLKI_Q | 0.050 | 0.164 | 0.194 | 0.166 | • | clk_ro_in__L2_I0 | A v -> Z ^ | INVERT_O | 0.072 | 0.041 | 0.234 | 0.207 | • | i_hitArbiterController2010a/reset_pileup_int_reg | CLK ^ | DFF_K | 0.072 | 0.000 | 0.235 | 0.207 | • +----------------------------------------------------------------------------------------------------------------+ • -------------------------------------------------------------------

signoff reg2reg setup (20130122) • ############################################################### • # Generated by: Cadence Encounter 09.12-s159_1 • # OS: Linux x86_64(Host ID lnxmics3) • # Generated on: Tue Jan 22 17:27:18 2013 • # Command: timeDesign -si -signoff -pathReports -drvReports -slackReports -numPaths 50 -prefix signoff -outDir ../report/timingReports • ############################################################### • Path 1: MET Setup Check with Pin i_hitArbiterController2010a/block_int_reg/CLK • Endpoint: i_hitArbiterController2010a/block_int_reg/D (v) checked with • leading edge of 'clk_ro_in' • Beginpoint: i_hitArbiterController2010a/daq_ready_int_reg/Q (^) triggered by • leading edge of 'clk_ro_in' • Path Groups: {reg2reg} • Other End Arrival Time 0.054 • - Setup 0.267 • + Phase Shift 2.380 • = Required Time 2.167 • - Arrival Time 0.944 • = Slack Time 1.222 • Clock Rise Edge 0.000 • + Source Insertion Delay 0.030 • = Beginpoint Arrival Time 0.030 • Timing Path: • +--------------------------------------------------------------------------------------------------------------+ • | Instance | Arc | Cell | Slew | Delay | Arrival | Required | • | | | | | | Time | Time | • |-----------------------------------------------+--------------+----------+-------+-------+---------+----------| • | | clk_ro_in ^ | | 0.000 | | 0.030 | 1.252 | • | clk_ro_in__L1_I0 | A ^ -> Z v | CLKI_Q | 0.050 | 0.164 | 0.194 | 1.416 | • | clk_ro_in__L2_I0 | A v -> Z ^ | INVERT_O | 0.072 | 0.041 | 0.234 | 1.457 | • | i_hitArbiterController2010a/daq_ready_int_reg | CLK ^ -> Q ^ | DFF_E | 0.069 | 0.286 | 0.520 | 1.743 | • | i_hitArbiterController2010a/p0882A | A ^ -> Z v | NAND2_B | 0.245 | 0.143 | 0.664 | 1.886 | • | i_hitArbiterController2010a/p1063A | A v -> Z ^ | NAND2_A | 0.238 | 0.167 | 0.830 | 2.053 | • | i_hitArbiterController2010a/p0013A | B ^ -> Z v | NOR2_B | 0.150 | 0.114 | 0.944 | 2.167 | • | i_hitArbiterController2010a/block_int_reg | D v | DFFSR_K | 0.150 | 0.000 | 0.944 | 2.167 | • +--------------------------------------------------------------------------------------------------------------+ • Clock Rise Edge 0.000 • + Source Insertion Delay -0.030 • = Beginpoint Arrival Time -0.030 • Other End Path: • +---------------------------------------------------------------------------------------------------------+ • | Instance | Arc | Cell | Slew | Delay | Arrival | Required | • | | | | | | Time | Time | • |-------------------------------------------+-------------+----------+-------+-------+---------+----------| • | | clk_ro_in ^ | | 0.000 | | -0.030 | -1.252 | • | clk_ro_in__L1_I0 | A ^ -> Z v | CLKI_Q | 0.017 | 0.067 | 0.037 | -1.186 | • | clk_ro_in__L2_I0 | A v -> Z ^ | INVERT_O | 0.022 | 0.018 | 0.054 | -1.168 | • | i_hitArbiterController2010a/block_int_reg | CLK ^ | DFFSR_K | 0.022 | 0.000 | 0.054 | -1.168 | • +---------------------------------------------------------------------------------------------------------+ • ---------------------------------------------------------- A. Kluge

signoff summary setup (20130122) • ############################################################### • # Generated by: Cadence Encounter 09.12-s159_1 • # OS: Linux x86_64(Host ID lnxmics3) • # Generated on: Tue Jan 22 17:27:18 2013 • # Command: timeDesign -si -signoff -pathReports -drvReports -slac... • ############################################################### • ------------------------------------------------------------ • timeDesign Summary • ------------------------------------------------------------ • +--------------------+---------+---------+---------+---------+---------+---------+ • | Setup mode | all | reg2reg | in2reg | reg2out | in2out | clkgate | • +--------------------+---------+---------+---------+---------+---------+---------+ • | WNS (ns):| 0.106 | 1.222 | 0.151 | 0.106 | 0.792 | N/A | • | TNS (ns):| 0.000 | 0.000 | 0.000 | 0.000 | 0.000 | N/A | • | Violating Paths:| 0 | 0 | 0 | 0 | 0 | N/A | • | All Paths:| 10 | 4 | 2 | 3 | 1 | N/A | • +--------------------+---------+---------+---------+---------+---------+---------+ • +----------------+-------------------------------+------------------+ • | | Real | Total | • | DRVs +------------------+------------+------------------| • | | Nr nets(terms) | Worst Vio | Nr nets(terms) | • +----------------+------------------+------------+------------------+ • | max_cap | 0 (0) | 0.000 | 0 (0) | • | max_tran | 0 (0) | 0.000 | 0 (0) | • | max_fanout | 0 (0) | 0 | 0 (0) | • +----------------+------------------+------------+------------------+ • Density: 107.746% • Total number of glitch violations: 0 • ------------------------------------------------------------

signoff summary hold 20130122 • ############################################################### • # Generated by: Cadence Encounter 09.12-s159_1 • # OS: Linux x86_64(Host ID lnxmics3) • # Generated on: Tue Jan 22 17:28:05 2013 • # Command: timeDesign -si -signoff -hold -pathReports -slackRepor... • ############################################################### • ------------------------------------------------------------ • timeDesign Summary • ------------------------------------------------------------ • +--------------------+---------+---------+---------+---------+---------+---------+ • | Hold mode | all | reg2reg | in2reg | reg2out | in2out | clkgate | • +--------------------+---------+---------+---------+---------+---------+---------+ • | WNS (ns):| -0.054 | -0.028 | -0.054 | 0.112 | N/A | N/A | • | TNS (ns):| -0.147 | -0.041 | -0.106 | 0.000 | N/A | N/A | • | Violating Paths:| 5 | 3 | 2 | 0 | N/A | N/A | • | All Paths:| 7 | 4 | 2 | 1 | N/A | N/A | • +--------------------+---------+---------+---------+---------+---------+---------+ • Density: 107.746% • Total number of glitch violations: 0 • ------------------------------------------------------------

signoff • AssuraDRC:x: 20130123 • CalibreDRC:20130123 • Assura LVS: 20130123 • CalibreLVS: 20130123

.lib files (20130122) • several .lib files have been created • only those are reasonable which are created when encounter is closed and restarted and createLibModels.tcl using saveModel is started. • sdf files and lib files have been compared for one signal: see next to pages • results seem coherent A. Kluge

notes on design flow • do not copy but take mklib in the project directory • ./mklib ‘name of digital block’ • will create directory structure from design_1 as in script on page 22. • following info is available for the script: • ------------------------------------------------------ • -- mklib -- by S. Bonacini and B. Van Koningsveld • ------------------------------------------------------ • Add in verilog the VDD,GND and IO pads. • What to do now: • - Copy your verilog files in ./digital/hitArbiter/syn/verilog [default name: hitArbiter.v] • - Edit ./digital/hitArbiter/syn/scripts/init.tcl setting the variables: CORE_CHIP, VERILOG_LIST, DFT • - Edit ./digital/hitArbiter/pnr/scripts/variables.tcl setting the variable: CORE_CHIP [default: CORE] • - A default sdc file is provided in ./digital/hitArbiter/syn/sdc/constraint.sdc [please set at least the clock signal] • - DFT [scan chain] port options are in ./digital/hitArbiter/syn/scripts/dft.tcl [default: off] • run synthesis in ./digital/hitArbiter/syn/work by launching ./run_rc • In case source is VHDL modify init.tcl: • remove files name from set ec::VERILOG_List and add to VHDL list • set _attribute hdl_language to vhdl • change read_hdl $ec::VHDL_LIST • modify import.tdl and change the floorplan values • run encounter until floorplan and do design/save/io and save template IO file to be modified • uncomment ioadIOfile ...save.io • - run PnR in ./digital/hitArbiter/pnr/work by launching encounter -replay ../scripts/all.tcl • or copy from me • /projects/IBM_CMOS8/gtk2010/V2.0/workAreas/akluge

change libraries to 1.2V • change timing libraries to 1.2 V • in: /projects/IBM_CMOS8/gtk2010/V3.0/workAreas/akluge/digital/hitArbiterAndController2010a/pnr/work • ln -s /vlsicad/micsoft/IBM_CMOS8_V1.8_DM_vcad/ibm_cmos8rf/std_cell/relDM/synopsys_1.2/ synopsys_std_cell_1.2 • change oa.conf in pnr/script • # original timing files • #set rda_Input(ui_timelib,max) { ./synopsys_std_cell/slow_v140_t125/IBM_CMOS8RF_CMOS8RF_SC_SLOW_V140_T125.lib \ • # ./synopsys_short_io/slow_v135_t125_pv162/IBM_CMOS8RF_BASE_SHORT_IO_SLOW_V135_T125_PV162.lib } • # • #set rda_Input(ui_timelib,min) { ./synopsys_std_cell/fast_v160_tm55/IBM_CMOS8RF_CMOS8RF_SC_FAST_V160_TM55.lib \ • # ./synopsys_short_io/fast_v165_tm40_pv363/IBM_CMOS8RF_BASE_SHORT_IO_FAST_V165_TM40_PV363.lib } • # end original timing files

change libraries to 1.2V • # 1.2 V timing files • set rda_Input(ui_timelib,max) { ./synopsys_std_cell_1.2/slow_v110_t125/IBM_CMOS8RF_STD_SLOW_V110_T125.lib \ • ./synopsys_short_io/slow_v108_t125_pv162/IBM_CMOS8RF_BASE_SHORT_IO_SLOW_V108_T125_PV162.lib } • set rda_Input(ui_timelib,min) { ./synopsys_std_cell_1.2/fast_v130_tm55/IBM_CMOS8RF_STD_V12_FAST_V130_TM55.lib \ • ./synopsys_short_io/fast_v132_tm40_pv363/IBM_CMOS8RF_BASE_SHORT_IO_FAST_V132_TM40_PV363.lib } • # end 1.2 V timing files • from 1.8 on change also mmc.view • #original files • #create_library_set -name libs_max -timing {./synopsys_std_cell/slow_v140_t125/IBM_CMOS8RF_CMOS8RF_SC_SLOW_V140_T125.lib ./synopsys_short_io/slow_v135_t125_pv162/IBM_CMOS8RF_BASE_SHORT_IO_SLOW_V135_T125_PV162.lib } -si {std_cell_ss_1.4v_125c.cdb} • #create_library_set -name libs_typ -timing {./synopsys_std_cell/typ_v150_t25/IBM_CMOS8RF_CMOS8RF_SC_TYP_V150_T25.lib ./synopsys_short_io/typ_v150_t25_pv250/IBM_CMOS8RF_BASE_SHORT_IO_TYP_V150_T25_PV250.lib } • #create_library_set -name libs_min -timing {./synopsys_std_cell/fast_v160_tm55/IBM_CMOS8RF_CMOS8RF_SC_FAST_V160_TM55.lib ./synopsys_short_io/fast_v165_tm40_pv363/IBM_CMOS8RF_BASE_SHORT_IO_FAST_V165_TM40_PV363.lib } -si {std_cell_ff_1.6v_m40c.cdb} • #end original files

change libraries to 1.2V • #changed for 1.2V operation • create_library_set -name libs_max -timing {./synopsys_std_cell_1.2/slow_v110_t125/IBM_CMOS8RF_STD_SLOW_V110_T125.lib ./synopsys_short_io/slow_v108_t125_pv162/IBM_CMOS8RF_BASE_SHORT_IO_SLOW_V108_T125_PV162.lib } -si {std_cell_ss_1.4v_125c.cdb} • create_library_set -name libs_typ -timing {./synopsys_std_cell_1.2/typ_v120_t25/IBM_CMOS8RF_STD_TYP_V120_T25.lib ./synopsys_short_io/typ_v120_t25_pv250/IBM_CMOS8RF_BASE_SHORT_IO_TYP_V120_T25_PV250.lib} • create_library_set -name libs_min -timing {./synopsys_std_cell_1.2/fast_v130_tm55/IBM_CMOS8RF_STD_V12_FAST_V130_TM55.lib ./synopsys_short_io/fast_v132_tm40_pv363/IBM_CMOS8RF_BASE_SHORT_IO_FAST_V132_TM40_PV363.lib } -si {std_cell_ff_1.6v_m40c.cdb} • # end changed for 1.2V operation • in mmmc.view and oa.conf link to std_cell_ff_1.6Vxxx.cdb files should be changed to 1.2V but does not exist. • change init.tcl in syn/script • # original settings • #set ec::LIBRARY "$IBM_PDK/ibm_cmos8rf/std_cell/rel$PDK_OPT/synopsys/slow_v140_t125/IBM_CMOS8RF_CMOS8RF_SC_SLOW_V140_T125.lib \ • # $IBM_PDK/ibm_cmos8rf/short_io/rel$PDK_OPT/synopsys/slow_v135_t125_pv162/IBM_CMOS8RF_BASE_SHORT_IO_SLOW_V135_T125_PV162.lib " • # • #end original setting • #1.2 V libraries

change libraries to 1.2V • set ec::LIBRARY "$IBM_PDK/ibm_cmos8rf/std_cell/rel$PDK_OPT/synopsys_1.2/slow_v110_t125/IBM_CMOS8RF_STD_SLOW_V110_T125.lib \ • $IBM_PDK/ibm_cmos8rf/short_io/rel$PDK_OPT/synopsys/slow_v108_t125_pv162/IBM_CMOS8RF_BASE_SHORT_IO_SLOW_V108_T125_PV162.lib " • #end 1.2V libraries

workflow synthesis and place & route • run: source /homedir/akluge/.xtra and gpak • syn: • in /projects/IBM_CMOS8/gtk2010/V4.0/workAreas/akluge/digital/qchip2010/syn/work/ ./run_rc • P&R: • in //projects/IBM_CMOS8/gtk2010/V4.0/workAreas/akluge/digital/qchip2010/pnr/work encounter –replay ../scripts/all.tcl • source ../script/power_analysis.tcl or run line by line manually to see graphically results • in same directory: run ‘abstract’ selecting • qchip2010 as library and qchip_abstract.options as options • select qchip2010 and move to block • clock on symbol for abstract run • run gate level synthesis with create_vcd_qchip.tcl on in ncsimQchipFunctional_cont.startupswitche on and run simulation for the time specified in command read_activity_file in power_analysis.tcl in pnr/script directory. • then run power_analysis.tcl in still open encounter window • closing encounter and reloading the dfm.enc does not run the power analysis error free. • then close encounter and re-open encounter and run createLibModels.tcl

workflow simulations • in pnr/work • run abstract import library HitArbiterAndControll2010a • import HitArbiterAndControll2010a_options.abstract • in akluge/. run • hdlCompileHitArbiterAndControll2010a.script

Assura DRC • Assura DRC • IBM_PDK > checking > Assura > DRC • rundirectory ./DRC (assura_drc_qchip) • rules file: /vlsicad/micsoft/IBM_CMOS8_V1.8_DM_vcad/IBM_PDK/cmrf8sf/V1.8.0.2DM/Assura/DRC/drc.rul (echo $techdir) • options: GridCheckBEOL_STACK_323 CELL • Assura density antenna checks • Assura run DRC • run directory ./ANT (./assura_ant_drc_qchip) • change technology field co cmos8sfTech • is greyed out and thus not possible ?[check Rule Set field to antenna] • click switch ames button and set the BEOL_STACK_323 ALL_CHECKS options

Calibre DRC • IBM_PDK Checking Calibre DRC menu • BEL_STACK:3_2_3, density local: off, design_type: celllast metal:MA, nummetal:8 OK • Rules Tab: /vlsicad/micsoft/IBM_CMOS8_V1.7_DM_vcad/IBM_PDK/cmrf8sf/relDM/Calibre/DRC/cmrf8sf.drc.cal • run directory: (calibre_drc_dll_state_machine) • Input tab: new directory OK • Output tab: • RunDRC: • Look at summary file

Assura LVS • assurarunLVS • set rundirectory field to ./assura_lvs_qchip2010 • change technology field to cmos8sfTech • set switches NO_SUBC_IN_GRLOGIC SBAR_feature • ruleset field to default • click OK • click watch logFile • after run click YES • From LVS debug • click on the Nets/Devices to peon Nets mismatch tool or devices mismatch tool • click view LVS Error Report • Go to LVS dir and check different files (.err, .cls, .sum)

Calibre LVS • IBM_PDK Checking Calibre LVS Menu • Default Runset (never appeared) • BEOL_STACK:3_2_3, cell, lastMetal: MA, #layers =8, No_subc_in_grlogic = true, use_resistance_multipliers: true • Rules tab: /vlsicad/micsoft/IBM_CMOS8_V1.8_DM_vcad/IBM_PDK/cmrf8sf/relDM/Calibre/DRC/cmrf8sf.drc.cal • Set DRCrundirectory calibre_lvs_qchip2010 • click inputs tab • Run LVS • in rundirectory check files

hdl files (akluge/digital/source_hitArbiterAndController2010a Test bench • 653 conf_hitArbiterAndController2010a_dfm.vhd • 5809 conf_hitArbiterAndController2010aX9_dfm.vhd • 1773 simulationPkg.vhd • 829 topSimulation.vhd • 195 verifyHitArbiter.vhd • 9259 total • 441 hitArbiterAndController2010a_dfm.v • 102 hitArbiterAndController2010a.v • 205 hitArbiterAndController2010aX9_noVddGnd.v • 224 hitArbiterController2010a.v • 138 hitArbiterManual2010a_noGndVddNS.v • 1110 total A. Kluge

Simulation log files A. Kluge

gate level simulation: min, 20130118 • *************** hit counters8 ********** • HitArbiter received hit from column (hit_in_count:) 425018 • Hits send to front-end (hit_count_before_frontend(index):) 425714 • --- • HitArbiter successfully assigns address (hit_out_count): 422061 • hit_out_count/hit_count_after_frontend: 9.930426E-01 • hit_out_count/hit_count_before_frontend: 9.914191E-01 • --- • Input to hitArbiter was not treated (hit_arbiter_time_out_counter): 130 • out of which are double_hit_shared: 46 • and out of which are no_hit_shared: 0 • each double_hit produces one NOTASSIGNED_DOUBLEADD error + 2 TIMEOUT, • each no_hit produces one NOTASSIGNED_DOUBLEADD error + 1 TIMEOUT+1PILEUP, • as the 2 inputs to the hitArbiter seem not to be treated and the output of the hitArbiter is not assigned. • In the data stream the address indicated the double hit and thus they can be treated as pileup. • The timeout_counter is thus overestimated can be corrected by • reducing 2*double_hit_counter and 1*no_hit_counter • Input to hitArbiter was not treated corrected(hit_arbiter_time_out_counter_corected): 38 • --- A. Kluge

gate level simulation: min • Arbiter found pileup (pileup_input_counter): 2827 • Successfully assigned pileupAddress (hit_out_pileup_count): 2827 • hit_arbiter_not_assigned_pileup_counter: 0 • hit_arbiter_not_assigned_address_counter: 46 • ------------------------------------ • All hits treated as pileups: pileup_input_counter+double_hit_shared+no_hit_shared: 2873 • hit_arbiter_time_out_counter_corrected = missing hits: 38 • hit_arbiter_time_out_counter_corrected/hit_count_before_frontend(index): 8.926180E-05 • all_pileup/hit_count_before_frontend(index): 6.748662E-03 • hit_out_count/hit_count_before_frontend: 9.914191E-01 • (hit_out_count+all_pileup)/hit_count_before_frontend: 9.981678E-01 • *********************************** A. Kluge

gate level simulation: min • ** Proc. report_latency_histogram RISING: • Pixel: 0 Bin: 0 Number_of_entries: 143592 Latency: 1 ns • Pixel: 0 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 0 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 0 Bin: 3 Number_of_entries: 0 Latency: 0 ns • Pixel: 1 Bin: 0 Number_of_entries: 114712 Latency: 1 ns • Pixel: 1 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 1 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 1 Bin: 3 Number_of_entries: 0 Latency: 0 ns • Pixel: 2 Bin: 0 Number_of_entries: 81485 Latency: 0.995 ns • Pixel: 2 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 2 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 2 Bin: 3 Number_of_entries: 0 Latency: 0 ns • Pixel: 3 Bin: 0 Number_of_entries: 52225 Latency: 0.994 ns • Pixel: 3 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 3 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 3 Bin: 3 Number_of_entries: 0 Latency: 0 ns • Pixel: 4 Bin: 0 Number_of_entries: 30047 Latency: 0.995 ns • Pixel: 4 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 4 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 4 Bin: 3 Number_of_entries: 0 Latency: 0 ns A. Kluge

gate level simulation: min • ** Proc. report_latency_histogram FALLING: • Pixel: 0 Bin: 0 Number_of_entries: 143592 Latency: 0.598 ns • Pixel: 0 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 0 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 0 Bin: 3 Number_of_entries: 0 Latency: 0 ns • Pixel: 1 Bin: 0 Number_of_entries: 114712 Latency: 0.598 ns • Pixel: 1 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 1 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 1 Bin: 3 Number_of_entries: 0 Latency: 0 ns • Pixel: 2 Bin: 0 Number_of_entries: 81485 Latency: 0.595 ns • Pixel: 2 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 2 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 2 Bin: 3 Number_of_entries: 0 Latency: 0 ns • Pixel: 3 Bin: 0 Number_of_entries: 52225 Latency: 0.591 ns • Pixel: 3 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 3 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 3 Bin: 3 Number_of_entries: 0 Latency: 0 ns • Pixel: 4 Bin: 0 Number_of_entries: 30047 Latency: 0.587 ns • Pixel: 4 Bin: 1 Number_of_entries: 0 Latency: 0 ns • Pixel: 4 Bin: 2 Number_of_entries: 0 Latency: 0 ns • Pixel: 4 Bin: 3 Number_of_entries: 0 Latency: 0 ns • *********************************** A. Kluge

gate level simulation: min • *************** Total hit counters afer all runs ********** • HitArbiter received hit from column (hit_in_count:) 425018 • Hits send to front-end (hit_count_before_frontend_total:) 425714 • --- • HitArbiter successfully assigns address (hit_out_count): 422061 • hit_out_count_total/hit_count_after_frontend_total: 9.930426E-01 • hit_out_count_total/hit_count_before_frontend_total: 9.914191E-01 • --- • Input to hitArbiter was not treated (hit_arbiter_time_out_counter): 130 • --- • Arbiter found pileup (pileup_input_counter_total): 2827 • Successfully assigned pileupAddress (hit_out_pileup_count_total): 2827 • hit_arbiter_not_assigned_pileup_counter_total: 0 • hit_arbiter_not_assigned_address_counter_total: 46 A. Kluge