Understanding Data Types in VHDL

370 likes | 642 Views

Learn about predefined and user-defined data types in VHDL, including scalar, composite, and physical types with examples. Understand how to declare and use data types effectively in your design.

Understanding Data Types in VHDL

E N D

Presentation Transcript

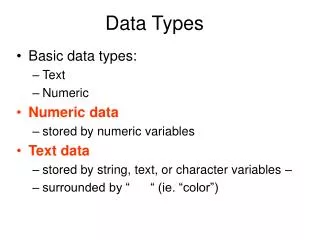

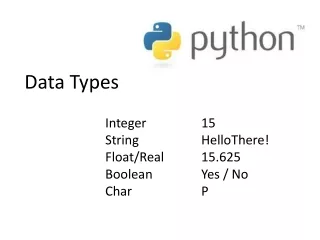

Data Types • Each data object has a type associated with it. • The type defines the set of values that the object can have and the set of operation that are allowed on it. DSD, USIT, GGSIPU

Data types defined in the standard package • Predefined data type are as follows: • Bit • Bit_vector • Boolean • Character • File_open_kind* • File_open_status* • Integer • Natural • Positive • Real • Severity_level • String • Time* DSD, USIT, GGSIPU

User-defined Types • The Syntax is TYPE identifier is Type_definition; Example: type small_int is range 0 to 1024; type my_word_length is range 31 downto 0; subtype data_word is my_word_length range 7 downto 0; DSD, USIT, GGSIPU

Data Types • A type declaration defines the name of the type and the range of the type. • Type declaration are allowed in package declaration sections, entity declaration sections, architecture declaration sections, subprogram declaration section and process declaration sections. DSD, USIT, GGSIPU

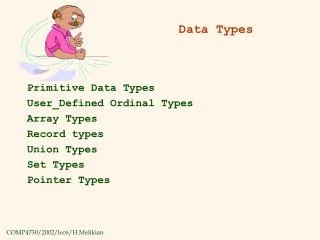

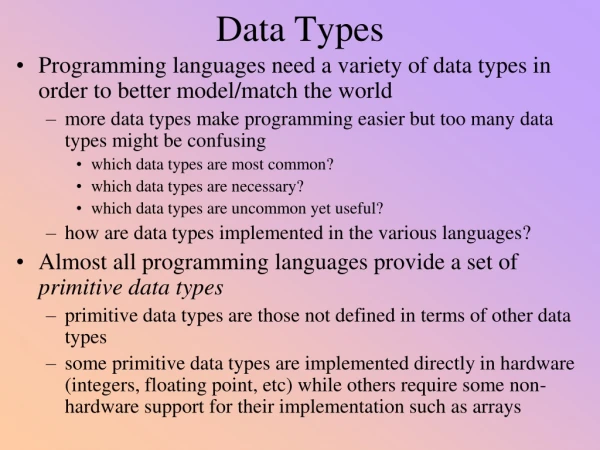

Types available in VHDL • Scalar types • Integer types • Real types • Enumerated • Physical • Composite Types • Arrays type • Records • Access Types (equivalent of pointers in C) • File types DSD, USIT, GGSIPU

Scalar Types • Scalar types describe objects that can hold , at most, one value at a time. • Integer Type • It is same as mathematical integers. • All of the normal predefined mathematical function apply to integer types. • Minimum Range: -2,147,483,647 to 12,147,483,647 DSD, USIT, GGSIPU

Example - Integer Architecture test of test is Begin Process (x) Variable a: integer; Begin a := 1; --ok a := -1 ; -- ok a := 1.0; -- error End process; End test; DSD, USIT, GGSIPU

Real Types • Real Types are used to declare objects that emulate mathematical real numbers. • Real number can be used to represent numbers out of the range of integer value as well as fractional values. • Minimum Range: -1.0E+38 to +1.0E+38 DSD, USIT, GGSIPU

Example – Real Types Architecture test of test is signal a : real; Begin a <= 1.0; -- ok a <= 1; -- error a <= -1.0E10; -- ok a <= 1.5E-20; --ok a <= 5.3 ns; -- error End test; DSD, USIT, GGSIPU

Enumerated types • Enumerated type is used to represent exactly the values required for a specific operation. • All of the values of an enumerated type are user-defined. • This values can be identifiers or single-character literals. • A typical example: TYPE fourval IS (‘x’, ‘0’, ‘1’, ‘z’); TYPE color IS (red,yellow, blue,green,orange); DSD, USIT, GGSIPU

IEEE standard 1164 Type std_logic is ( ‘U’, -- uninititalized ‘X’, -- forcing unknown ‘0’, -- forcing 0 ‘1’, -- forcing 1 ‘Z’, -- high impedence ‘W’, -- weak unknown ‘L’, -- weak 0 ‘H’, -- weak 1 ‘-’); -- don’t care DSD, USIT, GGSIPU

Physical Types • Physical types are used to represent physical quantities such as distance,current, time and so on. • A physical type provides for a base unit,and successive units are then defined in terms of this unit. • The smallest unit represented is one base unit. • The largest unit is determined by the range specified in physical type declaration. • TIME is a predefined physical types DSD, USIT, GGSIPU

Example – Physical Type Package example is type current is range 0 to 10000000000 units na; ua = 1000 na; -- nano amp ma = 1000 ua; -- micro amp a = 1000 ma; End units; type load_factor is (small, med, big); End example; DSD, USIT, GGSIPU

Architecture delay-cal of delay is Begin delay <= 10 ns when (load = small) else 20 ns when (load = med) else 30 ns when (load = big) else 40 ns; out-current <= 1000 ua when (load= small) else 1 ma when (load = med) else 100 ua; End delay-cal; DSD, USIT, GGSIPU

Predefined physical type - Time Type TIME is Range <implementation defined> units fs; --femtosecond ps = 1000 fs; -- picosecond ns = 1000 ps; -- nansecond us = 1000 ns; -- microsecond ms = 1000 us; -- millisecond sec = 1000 ms; -- second min = 60 sec; -- minute hr = 60 min; -- hour End units; DSD, USIT, GGSIPU

Composite Types • Arrays Type are groups of elements of the same type. • Arrays are useful for modeling linear structure such as RAMs and ROMs. • Record Types allow the grouping of elements of different types. • Record are useful for modeling data packets, instructions and so on. DSD, USIT, GGSIPU

Array Types • Array types group one or more elements of the same type together as a single object • Each element of the array can be accessed by one or more array indices. • Format of type declaration: TYPE data_bus IS array (0 to 31) of BIT; DSD, USIT, GGSIPU

Array slices and Ranges • Assignment of arrays preserves the left-to-right ordering regardless of the direction. • Example Signal x : std_logic_vector(0 to 3);--case 1 Signal y : std_logic_vector(3 downto 0); --case2 X <= “1010”; Y <= “0101”; DSD, USIT, GGSIPU

Cont.. • The assignment x<=y is equivalent to: X(0) <= Y(3); -- the left element X(1) <= y(2); X(2) <=Y(1); X(3) <=Y(0); -- the right elements The array range for case I in 0 to 3 loop, the elements of the array would be accessed from left to right. The array range for caseII in 3 downto 0 loop, the elements of the array would be accessed from right to left. DSD, USIT, GGSIPU

Multidimensional Array Type aggregate is array (range<>) of std_logic; Type identifier_a is array(range<>) of aggregate; Constant identifier_b : identifier_a := ((e1,e2…en), -- E1 (e1,e2,…en), --E2 . (e1,e2,…en)); --En DSD, USIT, GGSIPU

Example-Multidimensional arrays Library ieee; Use ieee.std_logic_1164.all; Package memory is constant width : integer := 3; constant memsize : integer := 7; Type data_out is array (0 to width) of std_logic; Type mem_data is arrary (0 to memsize) of data_out; End memory; DSD, USIT, GGSIPU

Library ieee; Use ieee.std_logic_1164.all; Use work.memory.all; Enity rom is -- ROM declaration port (addr : in integer; data : out data_out; cs : in std_logic; End rom; DSD, USIT, GGSIPU

Architecture basic of rom is constant z_state : data_out := (‘z’, ‘z’, ‘z’, ‘z’); constant x_state : data_out := (‘x’, ‘x’, ‘x’, ‘x’); constant rom_data : mem_data := ( (‘0’, ‘0’, ‘0’, ‘0’), (‘0’, ‘0’, ‘0’, ‘1’), (‘0’, ‘0’, ‘1’, ‘0’), (‘0’, ‘0’, ‘1’, ‘1’), (‘0’, ‘1’, ‘0’, ‘0’), (‘0’, ‘1’, ‘0’, ‘1’), (‘0’, ‘1’, ‘1’, ‘0’), (‘0’, ‘1’, ‘1’, ‘1’), ); Begin data <= rom_data (addr) when cs = ‘1’ else x_state when cs = ‘0’ else z_state; End basic; DSD, USIT, GGSIPU

Record Types • Record types group object of may types together as a single object. • Each element of the record can be accessed by its field name. • Record elements can include elements of any type, including arrays and records. • The elements of a record can be of the same type or different types. DSD, USIT, GGSIPU

Features of Records • A record is referenced by a single identifier. • Records are very useful to collapse multiple related elements into a single type so that record objects can be handle as a objects. • They are very useful in Bus Functional Models and test benches to pass a set of information to another process or another component. • Values can be assigned to a record type using aggregates in a manner similar to aggregates for arrays. DSD, USIT, GGSIPU

Limitation • Many synthesizers can compile records provided the elements of the record are of type Bit, bit_vector, boolean, std_ulogic, Std_ulogic_vector, integer or subtypes of these types. • However, most current synthesizers do not accept record aggregate assignments, and thus require individual assignment of the record elements. DSD, USIT, GGSIPU

Example - Records Type optype is (add,sub,mpy,div,jmp); Type instruction is Record -- declaration of record opcode : optype; -- field of record src : integer; dat : integer; End record; DSD, USIT, GGSIPU

Process (x) variable inst : instruction; variable source,dat : integer; variable operator : optype; Begin source := inst.src; -- ok dest := inst.src; -- ok source := inst.opcode; -- error operator := inst.opcode; --ok inst.src := dest; --ok DSD, USIT, GGSIPU

Access Types • Access types allow the designer to model objects of a dynamic nature. E.g. Queues, FIFO, Creating and Maintaining of a linked list. • Only variables can be declared as access types. • Used in Sequential processing • Not Synthesizeable statement. DSD, USIT, GGSIPU

Cont.. • Access types are used to declare values that access dynamically allocated variables. • Dynamically allocated variables are referenced, not by name, but by an access value that acts like a pointer to the variable. • Access types are used in the TextIO subprograms to read and write text strings. • Access types were efficiently used in VHDL in the functional modeling of large memories where fixed memory allocation is not realistic. DSD, USIT, GGSIPU

File Types • A file type allows declaration of objects that have a type FILE. • A file object type is actually a subset of the variable object type. • A variable object can be assigned with a variable assignment, while a file object cannot be assigned. • A file object can be read from, written to, and checked for end of file only with special procedure and functions. DSD, USIT, GGSIPU

Cont.. • File types are typically used to access files in the host environment. • File types are used to define objects representing files in the host system environment. • The value of a file object is the sequence of values contained in the host environment. • Package TextIO provides for the definition of file type TEXT as “type TEXT is file of string”. • TextIO package supports human readable IO. DSD, USIT, GGSIPU

Characters, Strings • To use character literal in a VHDL Code, one puts it in a single quotation mark. ‘a’, ‘B’, ‘,’ • A string of character are placed in double quotation marks: “aa”, “bb” Any printing character can be included inside a string. DSD, USIT, GGSIPU

Bit Strings • A bit-strings represents a sequence of bit values. E.g. Binary : B “1100_1001”, b “1001011” Hexagonal : X “C9”, X “4b” Octal : O “311”, o “113” DSD, USIT, GGSIPU