Sequential Logic

320 likes | 515 Views

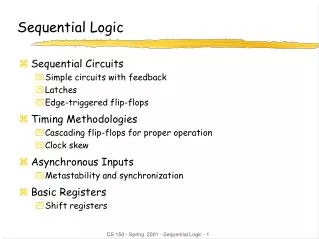

Sequential Logic. Lecture #9. 강의순서. FlipFlop Active-high Clock & asynchronous Clear Active-low Clock & asynchronous Clear Active-high Clock & asynchronous Preset Active-high Clock & asynchronous Clear & Preset Latch Shift Register Counter 4 bits Universal Counter : 74161

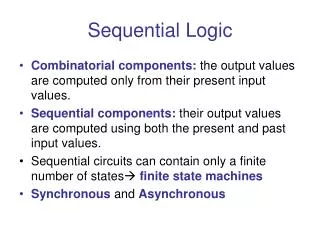

Sequential Logic

E N D

Presentation Transcript

Sequential Logic Lecture #9

강의순서 • FlipFlop • Active-high Clock & asynchronous Clear • Active-low Clock & asynchronous Clear • Active-high Clock & asynchronous Preset • Active-high Clock & asynchronous Clear & Preset • Latch • Shift Register • Counter • 4 bits Universal Counter : 74161 • Modulo 16 Up counter • Modulo 16 Down counter • Modulo 16 Up Down counter • 0-14 hold Up counter Sequential Logic

FlipFlop with active-high Clock & asynchronous Clear library ieee; use ieee.std_logic_1164.all; entity dff_1 is port( d, clk, nclr : in std_logic; q : out std_logic ); end dff_1 ; architecture a of dff_1 is begin process(nclr,clk) begin if( nclr='0') then q <='0'; elsif(clk'event and clk='1') then q <= d; end if; end process; end a; Sequential Logic

FlipFlop with active- low Clock & asynchronous Clear library ieee; use ieee.std_logic_1164.all; entity dff_fall_1 is port( d, clk, nclr : in std_logic; q : out std_logic ); end dff_fall_1 ; architecture a of dff_fall_1 is begin process(nclr,clk) begin if( nclr='0') then q <='0'; elsif(clk'event and clk=‘0') then q <= d; end if; end process; end a; Sequential Logic

FlipFlop with active-high Clock & asynchronous Preset library ieee; use ieee.std_logic_1164.all; entity dff_ preset_1 is port( d, clk, npre : in std_logic; q : out std_logic ); end dff_ preset_1 ; architecture a of dff_ preset_1 is begin process(npre,clk) begin if( npre='0') then q <=‘1'; elsif(clk'event and clk=‘1') then q <= d; end if; end process; end a; Sequential Logic

FlipFlop with active-high Clock & asynchronous Clear & Preset library ieee; use ieee.std_logic_1164.all; entity dff_ presetclr_1 is port( d, clk, npre,nclr : in std_logic; q : out std_logic ); end dff_ presetclr_1 ; architecture a of dff_ presetclr_1 is begin process(npre, nclr, clk) begin if( npre='0') then q <=‘1'; elsif( nclr='0') then q <=‘0'; elsif(clk'event and clk=‘1') then q <= d; end if; end process; end a; Sequential Logic

Latch library ieee; use ieee.std_logic_1164.all; entity latch_1 is port( d, ena : in std_logic; q : out std_logic ); end latch_1 ; architecture a of latch_1 is begin process(ena,d) begin if(ena=‘1') then q <= d; end if; end process; end a; Sequential Logic

Shift Register library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity shiftreg is port( d, clk,nclr : in std_logic; qa,qb : out std_logic ); end shiftreg; architecture a of shiftreg is signal tqa,tqb : std_logic; begin process(nclr,clk) begin if( nclr='0') then tqa <='0'; tqb <='0'; elsif(clk'event and clk='1') then tqa <= d; tqb <= tqa; end if; end process; qa<=tqa; qb<=tqb; end a; Sequential Logic

4 bits Universal Counter: 74161 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt161_4bits is port( d3,d2,d1,d0 : in std_logic; nld,ent,enp : in std_logic; clk,nclr : in std_logic; q3,q2,q1,q0 : out std_logic; rco : out std_logic); end cnt161_4bits; architecture a of cnt161_4bits is signal q : std_logic_vector( 3 downto 0); begin process(nclr,clk) variable d : std_logic_vector(3 downto 0); begin d := d3&d2&d1&d0; if( nclr='0') then q <="0000"; elsif(clk'event and clk='1') then if(nld='0') then q <= d; elsif(ent='1' and enp='1') then q <= q+'1'; end if; end if; end process; q3<=q(3); q2<=q(2); q1<=q(1); q0<=q(0); rco <= ent and q(3) and q(2) and q(1) and q(0); end a; 74161은 실제로 가장 널리 사용되는 4비트 카운터임 Sequential Logic

Modulo 16 Up Counter library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity mod16cnt is port( clk,nclr : in std_logic; q3,q2,q1,q0 : out std_logic); end mod16cnt; architecture a of mod16cnt is signal q : std_logic_vector( 3 downto 0); begin process(nclr,clk) begin if( nclr='0') then q <="0000"; elsif(clk'event and clk='1') then q <= q+'1'; end if; end process; q3<=q(3); q2<=q(2); q1<=q(1); q0<=q(0); end a; Sequential Logic

Modulo 16 Down Counter library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity mod16dncnt is port( clk,nclr : in std_logic; q3,q2,q1,q0 : out std_logic); end mod16dncnt; architecture a of mod16dncnt is signal q : std_logic_vector( 3 downto 0); begin process(nclr,clk) begin if( nclr='0') then q <="0000"; elsif(clk'event and clk='1') then q <= q-'1'; end if; end process; q3<=q(3); q2<=q(2); q1<=q(1); q0<=q(0); end a; Sequential Logic

Modulo 16 Up Down counter library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity UpDncnt4 is port( clk,nclr : in std_logic; UpDn : in std_logic; q3,q2,q1,q0 : out std_logic); end UpDncnt4; architecture a of UpDncnt4 is signal q : std_logic_vector( 3 downto 0); begin process(nclr,clk) begin if( nclr='0') then q <="0000"; elsif(clk'event and clk='1') then if( UpDn='1') then q <= q+'1'; else q <= q-'1'; end if; end if; end process; q3<=q(3); q2<=q(2); q1<=q(1); q0<=q(0); end a; 1 이면 증가 0 이면 감소 Sequential Logic

Modulo 15 Up Counter library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity mod15cnt is port( clk,nclr : in std_logic; q3,q2,q1,q0 : out std_logic); end mod15cnt; architecture a of mod15cnt is signal q : std_logic_vector( 3 downto 0); begin process(nclr,clk) begin if( nclr='0') then q <="0000"; elsif(clk'event and clk='1') then if( q="1110") then q<="0000"; else q <= q+'1'; end if; end if; end process; q3<=q(3); q2<=q(2); q1<=q(1); q0<=q(0); end a; 14에서 0 으로 증가 Sequential Logic

0-14 hold Up Counter library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity mod15holdcnt is port( clk,nclr : in std_logic; q3,q2,q1,q0 : out std_logic); end mod15holdcnt; architecture a of mod15holdcnt is signal q : std_logic_vector ( 3 downto 0); begin process(nclr,clk) begin if( nclr='0') then q <="0000"; elsif(clk'event and clk='1') then if( q=14) then q<=q; else q <= q+'1'; end if; end if; end process; q3<=q(3); q2<=q(2); q1<=q(1); q0<=q(0); end a; 14에서 정지 Sequential Logic

1bit Async load down counter Sequential Logic

4bit Async load down counter Sequential Logic

1bit Async Sync load down counter Sequential Logic

8bit Async sync load down counter Sequential Logic

State Machine - 강의순서 • Mealy Machine • Moore Machine Sequential Logic

State Machine - Mealy Machine • Mealy Machine • 현재의 상태(Current State)와 현재의 입력(Inputs)에 의해 출력이 결정 Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

State Machine - Moore Machine • Moore Machine • 현재의 상태(Current State)에 의해 출력(Outputs)이 결정 Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

0/00 S0 1/10 0/01 S1 1/00 Mealy Machine – VHDL Example 해석 1. WindowAct신호가 0에서 1로 변하는 순간에 RiseShot을 1로 만들고, 2. WindowAct신호가 1에서 0로 변하는 순간에 FallShot을 1로 만들어야함.. WindowAct / RiseShot, FallShot 입력 / 출력1, 출력2 Sequential Logic

Entity 문에 입출력이 표시. 같은 부분 Mealy Machine–Process 2개 사용 Library ieee; Use ieee.std_logic_1164.all; ENTITY RiseFallShot IS PORT( clk : IN STD_LOGIC; reset : IN STD_LOGIC; WindowAct : IN STD_LOGIC; RiseShot, FallShot : OUT STD_LOGIC); END RiseFallShot; ARCHITECTURE a OF RiseFallShot IS TYPE STATE_TYPE IS (s0, s1); SIGNAL state: STATE_TYPE; BEGIN PROCESS (clk, reset) BEGIN IF reset = '0' THEN state <= s0; ELSIF clk'EVENT AND clk = '1' THEN CASE state IS WHEN s0 => IF WindowAct='1' THEN state <= s1; ELSE state <= s0; END IF; WHEN others => IF WindowAct='0' THEN state <= s0; ELSE state <= s1; END IF; END CASE; END IF; END PROCESS; Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

같은 부분 Mealy Machine–Process 2개 사용 PROCESS(state, WindowAct) BEGIN if( state= s0 and WindowAct='1') then RiseShot <='1'; else RiseShot <='0'; end if; if( state= s1 and WindowAct='0') then FallShot <='1'; else FallShot <='0'; end if; END PROCESS; END a; Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

Entity 문에 입출력이 표시. 같은 부분 Mealy Machine–Process 3개 사용 library ieee; Use ieee.std_logic_1164.all; ENTITY RiseFallShot_v2 IS PORT( clk : IN STD_LOGIC; reset : IN STD_LOGIC; WindowAct : IN STD_LOGIC; RiseShot, FallShot : OUT STD_LOGIC); END RiseFallShot_v2; ARCHITECTURE a OF RiseFallShot_v2 IS TYPE STATE_TYPE IS (s0, s1); SIGNAL State, NextState: STATE_TYPE; BEGIN PROCESS (State, WindowAct) BEGIN CASE State IS WHEN s0 => IF WindowAct='1' THEN NextState <= s1; ELSE NextState <= s0; END IF; WHEN others => IF WindowAct='0' THEN NextState <= s0; ELSE NextState <= s1; END IF; END CASE; END PROCESS; Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

같은 부분 같은 부분 Mealy Machine–Process 3개 사용 PROCESS(reset,clk) BEGIN IF reset = '0' THEN State <= s0; ELSIF clk'EVENT AND clk = '1' THEN State <= NextState; END IF; END PROCESS; PROCESS(State,WindowAct) BEGIN if( State= s0 and WindowAct='1') then RiseShot <='1'; else RiseShot <='0'; end if; if( State= s1 and WindowAct='0') then FallShot <='1'; else FallShot <='0'; end if; END PROCESS; END a; Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

0 S0 000 1 1 S1 010 0 1 S2 101 Moore Machine – VHDL Example 상태 출력 입력 : WindowAct 출력 : y(2:0) 해석 1. WindowAct신호가 0에서는 상태의 변화가 없으며, 1인 구간에서는 상태의 변화가 S0->S1->S2->S0로 순환한다. 2. 출력신호 y(2:0)은 상태가 S0인 경우 “000”을 S1인 경우에는 “010”을 S2인 경우에는 “101”을 출력한다. Sequential Logic

Entity 문에 입출력이 표시. 같은 부분 Moore Machine–Process 2개 사용 Library ieee; Use ieee.std_logic_1164.all; ENTITY MooreMachine IS PORT( clk : IN STD_LOGIC; reset : IN STD_LOGIC; WindowAct : IN STD_LOGIC; y : OUT STD_LOGIC_vector(2 downto 0)); END MooreMachine; ARCHITECTURE a OF MooreMachine IS TYPE STATE_TYPE IS (s0, s1,s2); SIGNAL state: STATE_TYPE; BEGIN PROCESS (clk, reset) BEGIN IF reset = '0' THEN state <= s0; ELSIF clk'EVENT AND clk = '1' THEN CASE state IS WHEN s0 => IF WindowAct='1' THEN state <= s1; ELSE state <= s0; END IF; WHEN s1 => IF WindowAct='1' THEN state <= s2; ELSE state <= s1; END IF; WHEN others => IF WindowAct='1' THEN state <= s0; ELSE state <= s2; END IF; END CASE; END IF; END PROCESS; Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

같은 부분 Moore Machine–Process 2개 사용 PROCESS(state) BEGIN CASE state IS WHEN s0 => y <= "000"; WHEN s1 => y <= "010"; WHEN others => y <= "101"; END CASE; END PROCESS; END a; Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

Entity 문에 입출력이 표시. 같은 부분 Moore Machine–Process 3개 사용 Library ieee; Use ieee.std_logic_1164.all; ENTITY MooreMachine_v3 IS PORT( clk : IN STD_LOGIC; reset : IN STD_LOGIC; WindowAct : IN STD_LOGIC; y : OUT STD_LOGIC_vector(2 downto 0)); END MooreMachine_v3; ARCHITECTURE a OF MooreMachine_v3 IS TYPE STATE_TYPE IS (s0, s1,s2); SIGNAL state, NextState: STATE_TYPE; BEGIN PROCESS ( State, WindowAct) BEGIN CASE State IS WHEN s0 => IF WindowAct='1' THEN NextState <= s1; ELSE NextState <= s0; END IF; WHEN s1 => IF WindowAct='1' THEN NextState <= s2; ELSE NextState <= s1; END IF; WHEN others => IF WindowAct='1' THEN NextState <= s0; ELSE NextState <= s2; END IF; END CASE; END PROCESS; Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

같은 부분 같은 부분 Moore Machine–Process 3개 사용 PROCESS (clk, reset) BEGIN IF reset = '0' THEN state <= s0; ELSIF clk'EVENT AND clk = '1' THEN state <= NextState; END IF; END PROCESS; PROCESS(state) BEGIN CASE state IS WHEN s0 => y <= "000"; WHEN s1 => y <= "010"; WHEN others => y <= "101"; END CASE; END PROCESS; END a; Current State Combination Logic F/F Next State Inputs Combination Logic Outputs Sequential Logic

참고문헌 • PERRY, VHDL 4/E : PROGRAMMING BY EXAMPLE . • FLOYD, DIGITAL FUNDAMENTALS WITH VHDL . • ARMSTRONG,GRAY, VHDL DESIGN REPRESENTATION & SYNTHESIS. • SKHILL, VHDL FOR PROGRAMMABLE LOGIC . • PELLERIN, VHDL MADE EASY. • LEE, VHDL CODING & LOGIC SYNTHESIS WITH SYNOPSYS. Sequential Logic