Adder

200 likes | 605 Views

Adder. Discussion D6.2 Example 17. Full Adder (Appendix I). s i = c i ^ (a i ^ b i ). c i+1 = a i * b i + c i * (a i ^ b i ). -- Example 17a: 4-bit adder library IEEE; use IEEE.STD_LOGIC_1164. all ; use IEEE.STD_LOGIC_unsigned. all ; entity adder4a is port (

Adder

E N D

Presentation Transcript

Adder Discussion D6.2 Example 17

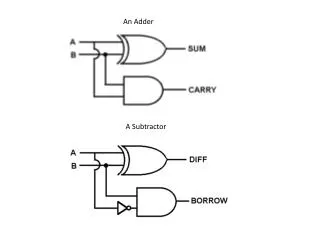

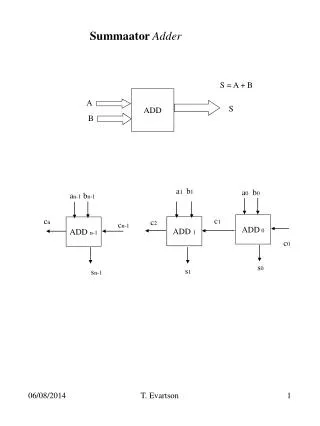

Full Adder (Appendix I) si = ci ^ (ai ^ bi) ci+1 = ai * bi + ci * (ai ^ bi)

-- Example 17a: 4-bit adder library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_unsigned.all; entity adder4a is port( a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); cf : out STD_LOGIC; ovf : out STD_LOGIC; s : out STD_LOGIC_VECTOR(3 downto 0) ); end adder4a;

architecture adder4a of adder4a is -- intermediate carries signal c: STD_LOGIC_VECTOR(4 downto 0); begin c(0) <= '0'; s <= a xor b xor c(3 downto 0); c(4 downto 1) <= (a and b) or (c(3 downto 0) and (a xor b)); cf <= c(4); ovf <= c(3) xor c(4); end adder4a;

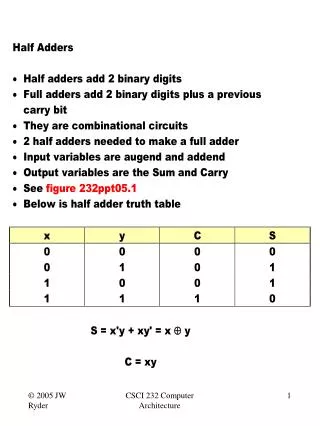

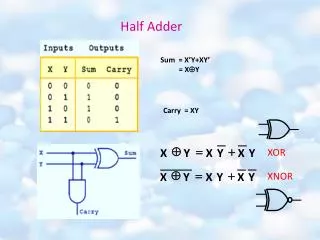

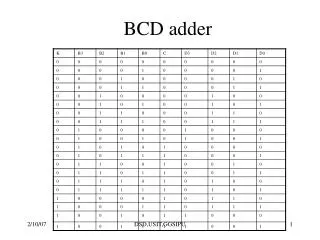

Full Adder Truth table Ci Si Ai Ci+1 Bi Behavior Ci+1:Si = Ci + Ai + Bi

Full Adder Block Diagram

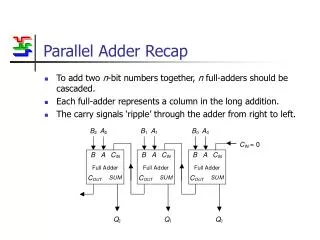

4-Bit Adder c 1 1 1 0 0:a 0 1 1 0 1 0:b 0 0 1 1 1 c4:s 1 0 1 0 0

-- Example 17a: 4-bit adder library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_unsigned.all; entity adder4b is port( a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); cf : out STD_LOGIC; ovf : out STD_LOGIC; s : out STD_LOGIC_VECTOR(3 downto 0) ); end adder4b;

architecture adder4b of adder4b is begin process(a,b) variable temp: STD_LOGIC_VECTOR(4 downto 0); variable sv: STD_LOGIC_VECTOR(3 downto 0); variable cfv: STD_LOGIC; begin temp := ('0' & a) + ('0' & b); sv := temp(3 downto 0); cfv := temp(4); ovf <= sv(3) xor a(3) xor b(3) xor cfv; cf <= cfv; s <= sv; end process; end adder4b; c 1 1 1 0 0:a 0 1 1 0 1 0:b 0 0 1 1 1 c4:s 1 0 1 0 0

N-Bit Adder -- Example 17c: 4-bit adder library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_unsigned.all; entity adder is generic(N:positive := 8); port( a : in STD_LOGIC_VECTOR(N-1 downto 0); b : in STD_LOGIC_VECTOR(N-1 downto 0); s : out STD_LOGIC_VECTOR(N-1 downto 0) ); end adder; architecture adder of adder is begin process(a,b) begin s <= a + b; end process; end adder;