CSC SLHC Electronics Upgrade Overview Stan Durkin

170 likes | 331 Views

CSC SLHC Electronics Upgrade Overview Stan Durkin April 23, 2004. The Cathode Strip Chamber Data Acquisition Electronics for CMS Nuclear Instruments and Methods in Physics Research Section A: Accelerators,

CSC SLHC Electronics Upgrade Overview Stan Durkin

E N D

Presentation Transcript

CSC SLHC Electronics Upgrade Overview Stan Durkin April 23, 2004 The Cathode Strip Chamber Data Acquisition Electronics for CMSNuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, Volume 600, Issue 3, Pages 661-672B. Bylsma, L. Durkin, J. Gilmore, J. Gu, T. Ling, C. Rush

Cathode Front End Board (CFEB) Input/Output Optimized for Precision Position Measurement • 5 cfebs/chamber, 96 strips/cfeb • 96 switch capacitors/channel • system is self triggering BUCKEYE (ASIC) - amplifies and shapes input pulse SCA (ASIC) - analog storage for 20 MHz sampled input pulse ADC - events with LVL1ACC digitized and sent to DAQ Motherboard (25 nsec/word) Comparator ASIC - generates trigger hit primitives from shaped pulse Controller FPGA - controls SCA storage and digitization

CFEB 50 nsec Sampling and Digitization • 6 Buckeyes serve 6 planes x 16 strips • 6 SCA’s serve 96 strips with 96 caps each • 50 nsec/sampling • no pedestals (< 1%) • 6 ADC’s (150 nsec digitization) • 12-bit + overflow bit • output 1 strip charge/25 nsec • 8 samples digitized for each of 96 strips • 6 SCA’s (96 caps/strip) • LVDS signaling • no cap pedestals • Control FPGA • 12 blocks of 8 caps each • grey-code (1 bit flip) addressing • (see movie for algorithm) Each Strip Amplifier Charge stored every 50 nsec in capacitors Beam Crossing PreLCT L1A·LCT Done 0.8sec 2.2sec 26sec 16 Cap Delay Cap Storage (Poisson) Cap Digization (Queue) For L1ALCT use LCT to choose which 8 capacitors to digitize Caps can be used for storage when all others in use 16 caps set aside for possible use

Simulation Single Strip Capacitor Usage A Nontrivial FPGA Algorithm Green – recently used Blue – set aside waiting for L1A Red- digitizing

Data Bottlenecks in CSC DAQ at SLHC • CFEB’s 96 Capacitors/channel is main DAQ rate limiter • DCC’s SLINK-64 is second DAQ rate limiter (already fixed) Simple Model CFEB Capacitor Storage Transfer to DMB Complete Beam Crossing LCT L1A·LCT 0.8sec 2.2sec 26sec 16 Cap Delay Cap Storage (Poisson) Cap Digization (Queue) Caps can be used for storage when all others in use For SLHC this is the main capacitor usage

Source strength K=5 (25 kHz/channel) Time (50ns/bin) Strip Channels Neutron/Gamma Background Dominates Event from X5 Beam test (Aug 99)

SCA Occupancy: LHC Rate Assumptions L1 Accept: 100 kHz LCT rate: 69 kHz per CFEB (worst case – ME1/1) Estimated LCT rate for 10**34 lumi (D. Acosta et al, 2001) Chamber Type LCT rate per CFEB (kHz) ME1/1 69 ME1/2 4 ME1/3 2 ME2/1 21 ME2/2 3 ME3/1 11 ME3/2 2 ME4/1 8 ME4/2 9 L1-LCT coincidence rate per CFEB: 100 kHz x 70 kHz x 75 ns = 0.5 kH Digitization time (with 6 ADCs on each CFEB) 16 channels x 16 samples/channel x 100 ns = 26 ms Problem! ‘ME1/1 LCT 96kHz/chamber (20 kHz) CMS Note 2002-007’ Hauser

ME1/1 Effective SCA Buffer Occupancy at SLHC • At SLHC: use same L1 accept rate assuming rates go up linearly. Maximum LCT rate is 700 kHz (ME1/1), L1-LCT match rate is 5.25 kHz. • Average number of LCTs during 5.2 ms (=6ms-0.8ms) holding time for 2-blocks: h=5.2x10-6x700x103=3.64 • Average number of L1-LCT matches during 26 ms digitization time: r=26x10-6x5.25x103=0.1365 • Probability of overuse of SCA: 0.09 !!!!!!!!!

Digital CFEB – A Nice Idea for the SLHC • Replace Conventional ADC and SCA storage with • Flash ADC and Digital Storage • New System Deadtimeless, Removes rate worries • Similar cost to old system • Fairly Radical Design – Couldn’t build 8 Years Ago

ME4/2 Linked to ME1/1 Upgrade? • New ME4/2 chambers need boards. • Propose 514 new cards ME1/1 • Old cards to populate ME4/2 Upgrade • ME1/1 • Handles highest particle flux • Most important for momentum • resolution. • Removes ganged strips in ME1/1a DCFEBs were designed for high Luminosity. We haven’t measured neutron and gamma background rates yet.

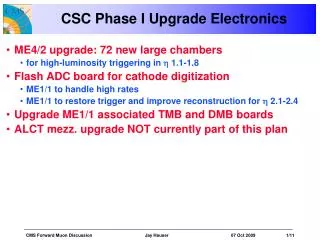

Overall Scope of Upgrade ME1/1 Electronics Upgrade 504 DCFEBs OSU 0.5 FTE 72 DMBs 72 TMB (d.c.)TAMU+ULCA 1.0FTE 8 MPC 72 LVDB (+more power) 72 LVMB 1008 Cables (default skewclear)

What this meeting is about When installing new ME1/1 chambers many new boards required Thus we make improvements: Design a 7 CFEB Trigger Board – new FPGA Design a 7 CFEB DAQMB (possibly single ASIC) Improve Board-Board Communication Present Skew-Clear Cable responsible for ME1/1 board failures ME1/1 at maximum allowed length Design a new Muon Port Card In this Meeting We are still in R&D stage Discuss design prototypes, progress, new ideas … Hope to try and define responsibilities. Get a feeling for a Timeline for prototypes and production

Digital CFEB R&D Board Designed to study (there will be issues): - Coupling single ended Buckeye Amp to bipolar flash SCAs - Fiber output versus Skewclear output Noise on Analog-Digital boards can be problems - use old PC boards analog isolation

Rates SLHC ME1/1 CFEB LCT*L1A Rate 5250 Hz CFEB Digitized Data Readout 67.2 Mbits/s Readout All Digitized Data 16 Gbit/s

Anode Cathode Trigger Primitives Cathode Trigger Primitives - Precision position (~0.5 cm/plane) - ASIC discriminator determines half strip • descriminator setting 16 bit DAC • minimum threshold 0.2 mV • timing spread over 3 Bx Cathode charges Test Beam Data 2004 Anode Trigger Primitives - Precision timing • Set fine timing (1 nsec) so signal • in a single Bx (see right) Anode hits Bx