Latch & Register Inference

190 likes | 227 Views

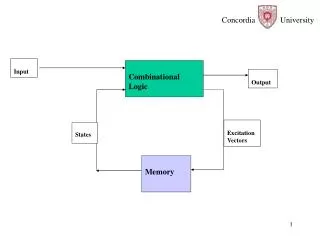

Latch & Register Inference. Latch Inference. In non-clocked processes, incompletely specified if and case statements cause synthesizers to infer latches for the variables and signals being assigned. --data_out is a latch Process(somesignal) Begin if (somesignal=‘1’) then

Latch & Register Inference

E N D

Presentation Transcript

Latch & Register Inference DSD,USIT,GGSIPU

Latch Inference • In non-clocked processes, incompletely specified if and case statements cause synthesizers to infer latches for the variables and signals being assigned. DSD,USIT,GGSIPU

--data_out is a latch Process(somesignal) Begin if (somesignal=‘1’) then data_out<= data_in; end if; End process; Process (somesignal) Begin case somesignal is when ‘0’ => data_out<= data_in; End case; End process; Example A latch is inferred for the signal data_out because is not assigned under all possible conditions. If the tested condition fails then data_out must hold the previous value. DSD,USIT,GGSIPU

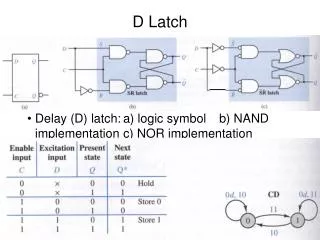

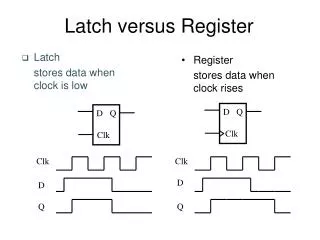

Definition • Basic Latch is a feedback connection of two NOR gates or two NAND gates, which can store one bit of information. It can be set to 1 using the S input and reset to 0 using the R input. • Gated Latch is a basic latch that includes input gating and a control input signal. The latch retains its existing state when the control input equals to 0. Its state may be changed when the control signal is equal to 1. DSD,USIT,GGSIPU

Sequential design library ieee; use ieee.std_logic_1164.all; entity ff is port ( s,r : in std_logic; q,qbar : out std_logic ); end ff; architecture behave of ff is begin process begin if (s = '0' and r = '0') then q <= '1'; qbar <= '0'; elsif (s = '0' and r = '1') then q <= '0'; qbar <= '1'; DSD,USIT,GGSIPU

elsif (s = '1' and r = '0') then q <= '1'; qbar <= '0'; else q <= '0'; qbar <= '0'; end if; end process; end behave; DSD,USIT,GGSIPU

D-flip flop library ieee; use ieee.std_logic_1164.all; entity dff is port (d, clk : in std_logic; q, qbar : out std_logic ); end dff; DSD,USIT,GGSIPU

architecture behave of dff is signal temp : std_logic; begin process (clk) begin if (clk'event and clk = '0') then temp <= d; end if; q <= temp; qbar <= not temp; end process; end behave; DSD,USIT,GGSIPU

SR flip-flop (process) library ieee; use ieee.std_logic_1164.all; entity ffclk is port ( s,r,clk : in std_logic; q,qbar : out std_logic ); end ffclk; DSD,USIT,GGSIPU

architecture behave of ffclk is signal temp,tempbar : std_logic; begin process (clk) begin if (clk = '1') then if (s = '0' and r = '0') then temp <= '1'; tempbar <= '0'; elsif (s = '0' and r = '1') then temp <= '0'; tempbar <= '1'; DSD,USIT,GGSIPU

elsif (s = '1' and r = '0') then temp <= '1'; tempbar <= '0'; else temp <= '0'; tempbar <= '0'; end if; else temp <= temp; tempbar <= tempbar; end if; q <= temp; qbar <= tempbar; end process; --q <= temp; --qbar <= tempbar; end behave; DSD,USIT,GGSIPU

counter library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity counter4bit is port (load,clear, clk : in std_logic; d : in std_logic_vector (3 downto 0); q : out std_logic_vector (3 downto 0) ); end counter4bit; DSD,USIT,GGSIPU

architecture behave of counter4bit is signal temp : std_logic_vector (3 downto 0); begin a: process (clk,load,clear,d) begin if (load = '1') then temp <= d; elsif (clear = '1') then temp <= "0000"; elsif (clk'event and clk = '1') then temp <= temp + "0001"; else DSD,USIT,GGSIPU

temp <= temp; end if; end process a; q <= temp; --b: process (clk) --begin --if (clk'event and clk = '1') then --q <= temp; --end if; --end process b; end behave; DSD,USIT,GGSIPU

With second process (b) DSD,USIT,GGSIPU