Reconfigurable Computing - VHDL – Types & Statements

360 likes | 553 Views

Reconfigurable Computing - VHDL – Types & Statements. John Morris The University of Auckland. Iolanthe on the Hauraki Gulf. You can give a variable an initial value when you declare it!. Types. VHDL is a fully-fledged programming language with a rich type system* Types include

Reconfigurable Computing - VHDL – Types & Statements

E N D

Presentation Transcript

Reconfigurable Computing -VHDL – Types & Statements John Morris The University of Auckland Iolanthe on the Hauraki Gulf

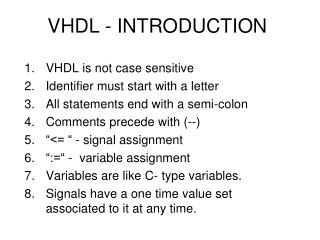

You can give a variable an initial value when youdeclare it! Types • VHDL is a fully-fledged programming language with a rich type system* • Types include • Those normally found in high level programming languages • integer, character, real, … • Example declarations VARIABLE a, b : integer := 0; x, y : real := 1.2e-06; p : character; *Computer scientist’s jargon for “You can make all the data types you need”

Types - Defining precision and range • Sub-types • Ada (and therefore VHDL) has a very flexible means of specifying exactly the requirements for representations (physical realizations) of numbers • This capability is important for efficient physical realizations • If you write VARIABLE x : integer; in your model,the synthesizer has to `guess’ how many bits of precision that you need for x! • However, if you write VARIABLE x : integer RANGE 0 .. 255;then the compiler knows that an 8-bit representation will be adequate! • Specifying the range of a data type is essential for efficient implementation • You don’t want the synthesizer to generate a 32-bit adder/subtracter/multiplier/… when an 8-bit one would do!

Literals – or constants • Most literals are similar to other languages • Integers – 0, 1, +1, -5, … • Reals – 0.0, 3.24, 1.0e+6, -6.5e-20, … • Characters – ‘A’, ‘a’, ‘(’, … • Strings (formally arrays of characters) – “clockA”, “data”, … • Numbers in non-decimal bases • For efficient digital circuit modeling, we need some way to specify numbers in binary, octal, hexadecimal • Ada and VHDL use a form: base#number# • Examples: • 2#001110#, 8#76771#, 16#a5a5#

Additional standard types • Boolean • Values are ‘true’ and ‘false’VARIABLE open, on : boolean := false; • Natural • The natural numbers from 0 →n • n is implementation defined • Commonly n=232-1 • Positive • Numbers from 1→n • Good practice tip! • Use boolean, natural and positive when appropriate • eg for counters use natural rather than integer • This helps the simulator detect errors in your program!

You probably should just add • this to every file – • You will need it most of the time! Libraries • VHDL’s standard defines a number of libraries or ‘package’s (using the Ada term) • The most useful is the IEEE 1164 standard logic package • To use it, add to the start of your program: • This library is just a VHDL package • You can usually find the source of it on your system • It is worthwhile looking through it …it provides many useful examples of VHDL capabilities! LIBRARY ieee;USE ieee.std_logic_1164.all;

IEEE 1164 standard logic package • std_logic is the most important type in this package • It’s an enumerated type: TYPE std_logic IS (‘U’, ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, ‘H’, ‘L’, ‘-’ );

IEEE 1164 standard logic package • You should always use std_logic in place of the (apparently) simpler bit type! • bit has values (‘0’, ‘1’) only • Always use the simplest possible type? • Not in this case!! • ‘Digital’ circuits are really analogue circuits in which we hope we can consider 0 and 1 values only! • Use of std_logic allows the simulator to pinpoint sources of error for you!

IEEE 1164 standard logic package • std_logic lets the simulator pinpoint errors for you! • ‘U’ – indicates a signal which has not yet been driven • Good design will ensure all signals are in known states at all times • A probable source of error in a properly designed circuit • ‘X’ → two drivers are driving a signal with ‘0’ and ‘1’ • A definite error! • Good design practice would ensure • All signals are defined in a reset phase • No ‘U’’s appear in the simulator waveforms (except in the initial reset phase) • Lines are never driven in opposite directions • Can cause destruction of drivers and catastrophic failure • High power consumption • Examine simulator traces for ‘X’ – there shouldn’t be any!

DeviceA DeviceB DeviceC IEEE 1164 standard logic package • Bus pull-up and pull-down resistors can be ‘inserted’ • Initialise a bus signal to ‘H’ or ‘L’: • ‘0’ or ‘1’ from any driver will override the weak ‘H’ or ‘L’: SIGNAL not_ready : std_logic := ‘H’; VDD 10k /ready IF seek_finished = ‘1’ THEN not_ready <= ‘0’; END IF;

IEEE 1164 standard logic package • Bus drivers can be disconnected • After a bus signal has been driven, it’s necessary to ‘release’ it: • eg once this device has driven not_ready, it should release it so that another device on the bus can assert (drive) it SIGNAL not_ready : std_logic := ‘H’; IF seek_finished = ‘1’ THEN not_ready <= ‘0’; END IF; … -- Perform device actions -- Now release not_ready not_ready <= ‘Z’;

Standard logic buses • VHDL arrays • Define an array with • In digital logic design, arrays of std_logic are very common, so a standard type is defined: • std_logic_vector is defined as an unconstrained array: • This means that you can supply the array bounds when youdeclare the array: TYPE bus8 IS ARRAY(0 TO 7) OF std_logic;data: bus8 := “ZZZZZZZZ”; data: std_logic_vector(0 TO 7) := “ZZZZZZZZ”; TYPE std_logic_vector IS ARRAY(integer RANGE <>) OF std_logic; We will learn more about unconstrained arrays later. Using them allows you to make complex models which you can use in many situations! cmd: std_logic_vector(0 TO 2) := “010”;address: std_logic_vector(0 TO 31);

Standard logic buses • VHDL supports arrays • Note that arrays can be defined with • ascending or • descending indices: • This could be considered convenientorit can lead to confusion! • Careful use of type attributes can make production and maintenance of VHDL models relatively painless! TYPE bus8 IS ARRAY(0 TO 7) OF std_logic;TYPE rev_bus8 is ARRAY(7 DOWNTO 0) OF std_logic;

Attributes • Attributes of variables and types are the values of properties of types and variables • For example, if you have defined an array: • then x’LOW and x’HIGH refer to the bounds of the array: • x’LOW is 0 • x’HIGH is 31 • IEEE numeric_std library • Note that in the IEEE numeric_std library, numbers are defined with the high index (MSB) first, so to make a 32 bit unsigned integer: TYPE unsigned32 IS ARRAY( 31 DOWNTO 0 ) OF std_logic; • When using this library, you must follow its conventions! x : std_logic_vector(0 to 31);

Attributes • Useful attributes are: • For all type of variables • LEFT, RIGHT – First or leftmost (last or rightmost) value of a variable • eg for a : NATURAL RANGE 0 TO 255;a’LEFT is 0 and a’RIGHT is 255 • RANGE – egx’RANGE is 0 to 31 • It can be used anywhere a range is needed • egdeclaring another array of the same size: • followed by • means that if you change the width of x, eg to change to a 64-bit bus, y will automatically follow • There are more attributes which apply only to signals – we will consider them later x : std_logic_vector(0 TO 31); y : std_logic_vector(x’RANGE);

Input can be anystd_logic vector • RANGE attribute produces the correct loop indices This is the first exampleof an algorithmic model. Note that the ‘code’ is embedded In a PROCESS block. Attributes • Now you can make a module which counts the bits in vectors of any size: ENTITY bitcounter IS PORT ( x: IN std_logic_vector; cnt : OUT natural ); END bitcounter; • The entity is • The architecture is ARCHITECTURE a OF bitcounter IS BEGIN PROCESS VARIABLE count : natural := 0; BEGIN FOR j IN x’RANGE LOOP IF x(j) = ‘1’ THEN count := count + 1; END LOOP; cnt <= count; END PROCESS; END a;

VHDL ‘Program’ statements • Process blocks • Placed inside architectures • Wrappers for program statements • Activated by changes in signals in sensitivity lists -- Template for a state machineARCHITECTURE fsm OF x IS BEGIN PROCESS( clk, reset ) BEGIN IF reset = ‘0’ THEN -- Initialization statements ELSE IF clk’EVENT AND clk = ‘1’ THEN -- Main state machine END IF; END IF; END PROCESS;END fsm; This template contains many features of PROCESS blocks,so we’ll examine it in more detail

VHDL ‘Program’ statements • This example assumes we have a clocked state machine with clk and reset inputs and several other inputs and outputs • The ENTITY is -- State machine entityENTITY x IS PORT ( … -- inputs and outputs -- needed by this SM clk, reset : IN std_logic );END ENTITY; outputs inputs clk -- Template for a state machineARCHITECTURE fsm OF x IS BEGIN PROCESS( clk, reset ) … END PROCESS; END fsm; reset

VHDL ‘Program’ statements PROCESS blocks start with PROCESS( sensitivity list ) and end with END PROCESS; • Process blocks -- Template for a state machineARCHITECTURE fsm OF x IS BEGIN PROCESS( clk, reset ) BEGIN IF reset = ‘0’ THEN -- Initialization statements ELSE IF clk’EVENT AND clk = ‘1’ THEN -- Main state machine END IF; END IF; END PROCESS; END fsm; The PROCESS blocks is entered (activated)on a change in any signal in the sensitivitylist. In this case, every change of reset or clkwill cause the PROCESS block to be enteredand evaluated.

VHDL ‘Program’ statements • Process blocks Here is an IF … THEN … ELSE … END IF;block. -- Template for a state machineARCHITECTURE fsm OF x IS BEGIN PROCESS( clk, reset ) BEGIN IF reset = ‘0’ THEN -- Initialization statements ELSE IF clk’EVENT AND clk = ‘1’ THEN -- Main state machine END IF; END IF; END PROCESS; END fsm; Note the END IF pattern – Most VHDL blocks are like this.

VHDL ‘Program’ statements • Process blocks Then we have a nested IF .. It could also have been writtenIF reset = ‘0’ THEN ELSIF clk’EVENT .. THEN … END IF; slightly more compact code -- Template for a state machineARCHITECTURE fsm OF x IS BEGIN PROCESS( clk, reset ) BEGIN IF reset = ‘0’ THEN -- Initialization statements ELSE IF clk’EVENT AND clk = ‘1’ THEN -- Main state machine END IF; END IF; END PROCESS; END fsm;

VHDL ‘Program’ statements • Process blocks Finally note the IF clk’EVENT and clk = ‘1’ pattern – Although this is not the only way to definea synchronous circuit in which state changesare triggered by rising clock edges,this pattern is recognized by most synthesizers. -- Template for a state machineARCHITECTURE fsm OF x IS BEGIN PROCESS( clk, reset ) BEGIN IF reset = ‘0’ THEN -- Initialization statements ELSE IF clk’EVENT AND clk = ‘1’ THEN -- Main state machine END IF; END IF; END PROCESS; END fsm; clk’EVENT EVENT is an attributeof a SIGNAL – It’s TRUE when an event (change) to thesignal value has occurred.

VHDL ‘Program statements’ • IF … • Very similar to the if … then … else … blocks of most high level languages • The else branch is optional • Condition must, naturally, evaluate to TRUE or FALSE • The relational operators are AND, OR, XOR, NOT IF condition THEN -- Statements executed if condition is TRUE ELSE -- Statements executed if condition is FALSE END IF; IF condition THEN -- Statements executed if condition is TRUEEND IF;

VHDL ‘Program statements’ • IF … • Nested if … - a useful shorthand for lazy typists! IF condition1 THEN -- Statements executed if condition1 is TRUE ELSIF condition2 THEN -- Statements executed if condition2 is TRUE ELSIF condition3 THEN -- Statements executed if condition3 is TRUE ELSE -- Statements executed if all conditions are FALSEEND IF;

VHDL ‘Program statements’ • LOOPS • VHDL loops - a few more options than C’s simple structures! • The simplest loop continues until an EXIT is generated • There must be at least one WAIT • A WAIT condition might be something like LOOP WAIT UNTIL condition1; -- statements EXIT WHEN condition2;END LOOP; LOOP WAIT UNTIL clk = ‘1’; -- statementsEND LOOP;

Wait statements • There are 3 variants of the WAIT statement • wait until condition • Waits until condition is true • Example • wait time • Waits for a specified time • Example • Note that time is an inbuilt type in VHDLIt has integer values and units fs, ns, us, ms, sec, … WAIT UNTIL request = ‘1’; WAIT 5 ns; Whilst it is useful to simulate propagation delays in simulation, most synthesizers cannot handle wait time!

Wait statements • There are 3 variants of the WAIT statement • wait on signal • Waits until some signal changes • Example • Note that if a process has a wait statement, it cannot have a sensitivity list • The sensitivity list performs a similar function to wait on .. • wait statements are most useful in test benches • Include them in models simulating actual devices to simulate delays in the real device WAIT ON bus_grant; Again, most synthesizers cannot handle wait on signal!

While loops • VHDL supports a while loop WHILE condition LOOP -- statements -- may include exit statements END LOOP;

for loops • VHDL supports a powerful for loop • Example • Rules • identifier should not be declared elsewhere • It’s implicitly declared to have the type specified by range • It has no value (cannot be used) outside the loop FOR identifier IN range LOOP -- statements -- may include exit statements END LOOP; FOR j IN 0 TO 14 LOOP sum := sum + a(j); END LOOP;

for loops • VHDL supports a powerful for loop • The power lies in the possible ways that range can be used! • We already saw that an array range can be used or you can use the type’RANGE TYPE bit32 IS ARRAY (0 TO 31) OF std_logic; VARIABLE x : bit32; …FOR J IN x’RANGE LOOP IF x(J) = ‘1’ THEN EXIT; END LOOP; TYPE bit32 IS ARRAY (0 TO 31) OF std_logic; VARIABLE x : bit32;FOR J IN bit32’RANGE LOOP IF x(J) = ‘1’ THEN EXIT; END LOOP;

for loops • VHDL supports a powerful for loop • You can parameterize a whole design through types • For example, you want to build circuits that handle words of various lengths • Define a subtype wordsize: • This means that changing the definition of wordsize can change a whole design to use shorter or longer words • Combined, of course, with extensive use of attributes like‘RANGE, ‘LEFT, ‘RIGHT, … • More elegant than defining constants for 0 and 31 ! SUBTYPE wordsize IS natural RANGE 0 TO 31; TYPE word IS ARRAY (wordsize) OF std_logic; …FOR J IN wordsize LOOP IF x(J) = ‘1’ THEN EXIT; END LOOP;

case statements • case statements make state machines simple! • … and a lot of other applications! • Rules • expression must evaluate to an integer, an enumerated type or a one-dimensional array, such as std_logic_vector. • expression is evaluated and compared to the value of each of the choices. The when clause corresponding to the matching choice will be executed. CASE expression IS WHEN choice1 => statements; WHEN choice2 => statements; WHEN OTHERS => statements; END CASE;

case statements • case statements make state machines simple! • … and a lot of other applications! • Rules (cont) • choices must not overlap, ie only one should match. • OTHERS must be present unless all possible cases are covered by choices. CASE expression IS WHEN choice1 => statements; WHEN choice2 => statements; WHEN OTHERS => statements; END CASE;

case statements • Examples • Simple state machine TYPE states ARE (A, B, C, D); SIGNAL s : states; IF reset = ‘0’ THEN s <= A; ELSIF clk’EVENT AND clk = ‘1’ THEN CASE s IS WHEN A => -- Set outputs for state A IF next = ‘1’ THEN s <= B; WHEN B => -- Set outputs for state B IF next = ‘1’ THEN s <= C; WHEN OTHERS => s <= A; END CASE; END IF; Some details omitted, egPROCESS block!

Could have std_logic_vector here! … and bit patterns here“111111…11111”, “111111…10000” here! case statements • Examples • Address selector SIGNAL address : INTEGER; ... PROCESS ( clk ) BEGIN CASE address IS WHEN 16#ffff# => device <= ‘0’; -- select device 1 WHEN 16#fff0# => device <= ‘1’; -- select device 2 WHEN OTHERS => device <= ‘Z’; -- disconnect device END CASE; END PROCESS;