DCM Location and clock distribution

190 likes | 376 Views

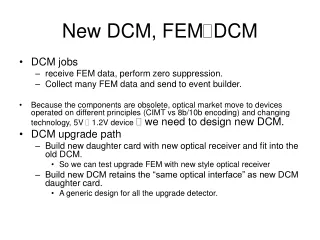

DCM Location and clock distribution. DCM and clock distribution 1. Xilinx Digital Clock Manager. Xilinx Core Generator. Xilinx Core Generator Project. Xilinx Gore Generator Project Setup 1. Xilinx Core Generator Project Setup 2. Generating Single DCM module. DCM Setup 1. DCM Setup 2.

DCM Location and clock distribution

E N D

Presentation Transcript

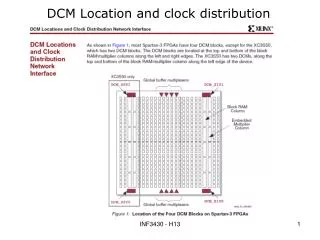

DCM Location and clock distribution INF3430 - H13

DCM and clock distribution 1 INF3430 - H13

Xilinx Digital Clock Manager INF3430 - H13

Xilinx Core Generator INF3430 - H13

Xilinx Core Generator Project INF3430 - H13

Xilinx Gore Generator Project Setup 1 INF3430 - H13

Xilinx Core Generator Project Setup 2 INF3430 - H13

Generating Single DCM module INF3430 - H13

DCM Setup 1 INF3430 - H13

DCM Setup 2 INF3430 - H13

DCM Setup 3 INF3430 - H13

DCM Setup 4 INF3430 - H13

DCM Setup 5 INF3430 - H13

library ieee; use ieee.std_logic_1164.ALL; use ieee.numeric_std.ALL; library UNISIM; use UNISIM.Vcomponents.ALL; entity clkmng is port ( CLKIN_IN : in std_logic; RST_IN : in std_logic; CLKFX_OUT : out std_logic; CLK0_OUT : out std_logic; LOCKED_OUT : out std_logic); end clkmng; DCM module Entity INF3430 - H13

architecture BEHAVIORAL of clkmng is signal CLKFB_IN : std_logic; signal CLKFX_BUF : std_logic; signal CLK0_BUF : std_logic; …… begin CLK0_OUT <= CLKFB_IN; CLKFX_BUFG_INST : BUFG port map (I=>CLKFX_BUF, O=>CLKFX_OUT); CLK0_BUFG_INST : BUFG port map (I=>CLK0_BUF, O=>CLKFB_IN); DCM_INST : DCM generic map( CLK_FEEDBACK => "1X", …… ) port map(CLKFB => CLKFB_IN, CLKIN => CLKIN_IN, …… RST => RST_IN, …… CLKFX => CLKFX_BUF, …… CLK0 => CLK0_BUF, …… LOCKED => LOCKED_OUT, …… ); < Evnt. Generert Reset logic; se slide 18-19 > end BEHAVIORAL; DCM module Architecture INF3430 - H13

entity cru is port ( arst : in std_logic; -- Asynch. reset refclk : in std_logic; -- Reference clock; 50 MHz rst : out std_logic; -- Synchronized arst_n for mclk rst_div : out std_logic; -- Synchronized arst_n for mclk_div128 mclk : out std_logic; -- Master clock; 50 MHz pclk : out std_logic; -- Processor clock; 100 MHz mclk_div : out std_logic -- Master clock div. by 128. ); end cru CRU med clkmng module Entity INF3430 - H13

: : clkmng_0: clkmng port map ( CLKIN_IN => refclk, RST_IN => arst, CLKFX_OUT => pclk, CLK0_OUT => mclk_i, LOCKED_OUT => open); -- Removed in architecture str2 with DCM -- -- bufg_0: bufg -- port map ( -- i => refclk, -- o => mclk_i); : : CRU with clkmng module Architecture INF3430 - H13

DCM med ekstra reset logic del 1 INF3430 - H13

DCM med ekstra reset logic del 2 INF3430 - H13