Memory Systems Caching

220 likes | 376 Views

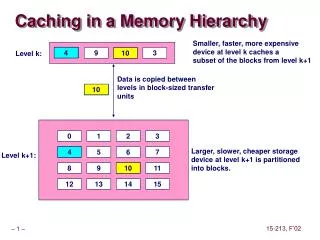

Memory Systems Caching. Lecture 24 Digital Design and Computer Architecture Harris & Harris Morgan Kaufmann / Elsevier, 2007. The Memory Interface. The Ideal Memory System. Memory Hierarchy. Memory Performance. Hit: is found in that level of memory hierarchy

Memory Systems Caching

E N D

Presentation Transcript

Memory SystemsCaching Lecture 24 Digital Design and Computer Architecture Harris & Harris Morgan Kaufmann / Elsevier, 2007

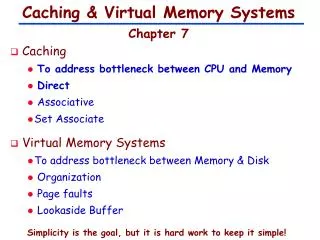

Memory Performance • Hit: is found in that level of memory hierarchy • Miss: is not found (must go to the next level of memory hierarchy)

Caches A safe place to hide things • What data is stored? • How is the data found? • What data is replaced?

Direct-Mapped Cache Performance # MIPS assembly code addi $t0, $0, 5 loop: beq $t0, $0, done lw $t1, 0x4($0) lw $t2, 0xC($0) lw $t3, 0x8($0) addi $t0, $t0, -1 j loop done:

Direct-Mapped Cache Performance # MIPS assembly code addi $t0, $0, 5 loop: beq $t0, $0, done lw $t1, 0x4($0) lw $t2, 0x24($0) addi $t0, $t0, -1 j loop done:

N-way Set Associative Performance # MIPS assembly code addi $t0, $0, 5 loop: beq $t0, $0, done lw $t1, 0x4($0) lw $t2, 0x24($0) addi $t0, $t0, -1 j loop done:

Direct-Mapped Cache Performance # MIPS assembly code addi $t0, $0, 5 loop: beq $t0, $0, done lw $t1, 0x4($0) lw $t2, 0xC($0) lw $t3, 0x8($0) addi $t0, $t0, -1 j loop done:

LRU Replacement # MIPS assembly lw $t0, 0x04($0) lw $t1, 0x24($0) lw $t2, 0x54($0)

Caching Summary • Temporal and spatial locality • LRU or pseudo-LRU replacement • Cache Parameters: • C = capacity • b = block size • B = # blocks = C/b • S = number of sets • N = # blocks in a set (# of ways)

Next Time Virtual Memory