Leon Processor Overview with Key Features and Synthesis Instructions

220 likes | 294 Views

Explore the characteristics, configuration options, and synthesis guidelines for the Leon processor designed by Rodolfo Jardim de Azevedo. This processor boasts a RISC architecture with SPARC V8 standard, 32-bit word, and VHDL-87 description. Learn about the AMBA bus, memory controller, manual configuration, synthesis scripts, Xilinx FPGA tools for synthesis, and simulation with ModelSim. The SPARC features include a detailed instruction set, memory region support, and big-endian format. Discover the register organization, instruction format, and specific registers of the Leon processor.

Leon Processor Overview with Key Features and Synthesis Instructions

E N D

Presentation Transcript

O Processador Leon Rodolfo Jardim de Azevedo

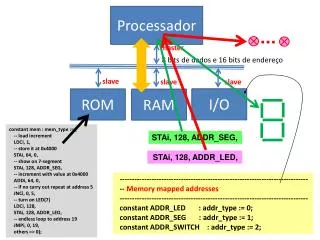

Características Básicas • Processador RISC • Padrão SPARC V8 (IEEE-1754) • Palavra de 32 bits • Descrição em VHDL-87 • Barramento AMBA (AHB e APB) para interligação de periféricos • Controlador de memória (SRAM e DRAM)

Configuração do Processador • Duas alternativas • Interface gráfica make xconfig (Linux) make wconfig (Windows + cygwin) • Edição manual dos arquivos device.vhd e target.vhd

Interface Gráfica • Interface de configuração similar ao do kernel do Linux

Configuração Manual • target.vhd • Declara as estruturas de configuração • device.vhd • Cria a estrutura confque armazena a configuração do leon • A constante tkconfig é gerada automaticamente pela interface gráfica.

Síntese • O diretório syn possui scripts de síntese para diversas ferramentas • Arquivo para Leonardo: leon.tcl (sem informações sobre tecnologia) read -dont_elaborate ../leon/amba.vhd read -dont_elaborate ../leon/target.vhd read -dont_elaborate ../leon/device.vhd read -dont_elaborate ../leon/config.vhd read -dont_elaborate ../leon/sparcv8.vhd read -dont_elaborate ../leon/iface.vhd read -dont_elaborate ../leon/macro.vhd ... read -dont_elaborate ../leon/mcore.vhd read -dont_elaborate ../leon/leon.vhd elaborate leon -architecture rtl

Síntese (cont.) • Informações sobre tecnologia no início do arquivo • FPGA Xilinx XCV800 do kit da XESS set part v800hq240 set process 4 set wire_table xcv800-4_wc load_library xcv

Síntese (cont.) read -dont_elaborate ./xsv800.vhd elaborate xsv800 -architecture rtl set xilinx_exec_path /home/lsc/xilinx/bin/sol set edif_write_arrays FALSE # Comandos para contornar incompatibilidades com a Xilinx set register2register 80 set input2register 80 set register2output 80 optimize .work.xsv800.rtl -target xcv -chip -delay -effort quick optimize_timing .work.xsv800.rtl # Output report_area xsv800.area -cell_usage -all_leafs report_delay xsv800.delay -num_paths 1 -critical_paths -clock_frequency auto_write -downto xcv xsv800.edf

Ferramentas da Xilinx • Ferramentas de linha de comando: ngdbuild -p xcv800-4-hq240 -uc xsv800.ucf xsv800.edf xsv800.ngd map -p xcv800-4-hq240 -o xsv800.ncd xsv800.ngd xsv800.pcf par -w xsv800.ncd xsv800.ncd xsv800.pcf trce -skew xsv800.ncd xsv800.pcf -o xsv800.twr -xml xsv800.twx bitgen xsv800.ncd -d -w

Simulação • Utilizando o ModelSim basta executar o comando make no diretório raiz da distribuição e chamar o simulador • Diretórios: • tbench: Código VHDL do Test Bench do Leon • tsource: Código em C para teste do processador • leon: Descrição VHDL do processador

Kit da XESS • Utilitários com interface gráfica para Windows e versões de linha de comando para Linux • gxsload ou xsload: Transferência de arquivos para a placa através da interface paralela • gxsetclk ou xsetclk: Altera a freqüência do clock da placa (entre 10KHz e 100MHz)

Características SPARC • Conjunto maior de instruções • Mais instruções de salto • Instruções para ativar código de condição (cc) • Suporte a regiões específicas de memória (ASI – Address Space Identifier) • Imediato de 30 bits no CALL • Big endian

Instruções (notação) • rs1 e rs2 são as origens • rd é o registrador destino • ADD rs1, rs2, rd rd = rs1 + rs2 Ex.: ADD %i3, %i4, %o0 • ADD rs1, 100, rd rd = rs1 + 100 Ex.: ADD %i3, 100, %o0

Registradores • Banco de Registradores organizado em janelas r[0]..r[7] (global) CWP + 1 CWP Current Window CWP - 1 Restore, RETT SAVE, trap