The Evolution of Dynamic Random Access Memory (DRAM)

260 likes | 796 Views

The Evolution of Dynamic Random Access Memory (DRAM). CS 350 Computer Organization and Architecture Spring 2002 Section 1 Nicole Chung Brian C. Hoffman Joel D. Throckmorton Thomas C. Wear. DRAM. Manufacturer: IBM Speed: 35-200ns

The Evolution of Dynamic Random Access Memory (DRAM)

E N D

Presentation Transcript

The Evolution of Dynamic Random Access Memory(DRAM) CS 350 Computer Organization and ArchitectureSpring 2002Section 1Nicole ChungBrian C. HoffmanJoel D. ThrockmortonThomas C. Wear

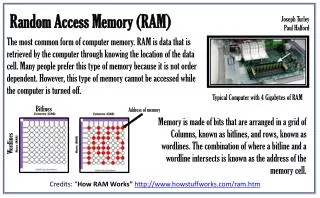

DRAM • Manufacturer: IBM Speed: 35-200ns • Year Introduced: 1969 Frequency: 4.77-40MHz • Burst Timing: 5-5-5-5 Pins: SOJ(20,24,26) • Voltage: +5v,-5v,+12v

DRAM • Similar to manufacturing processors • Multiplexed address lines • Separate data inputs and outputs • Three control signals • Two primary effects

FPM DRAM • Manufacturer: many Speed: 50ns • Year Introduced: 1987 Frequency: 16-66 MHz • Burst Timing: 5-3-3-3 Pins: 72/168 • Voltage: 5.0v Bandwidth: 188.71MBs

FPM DRAM • Simple DRAM slightly slower than FPM • How it works • “Safe” • Used primarily for main system memories • Not well-suited for high-performance video applications

EDODRAM • Extended Data Output Random Access Memory • Introduced in 1994, Improvement over FPM • Up to 40% increase in access time, over FPM • EDO shortens the read cycle between the memory and the CPU • EDO chips still hold data valid after the signal that “strobes” the column address goes inactive. Meaning, the CPU can perform other operations while memory is being accessed.

EDODRAM • EDODRAM runs asynchronously w/ the CPU clock • SDRAM has taken the place of EDODRAM • There is no difference between SDRAM and EDO at bus speeds at or below 83MHz. • EDO timing: 5-2-2-2 at 66 MHz

BEDODRAM • Burst EDODRAM • Introduced in 1995 • Read/write cycles were batched in bursts of four • “The memory bursts wrap around on a four byte boundary which means that only the two least significant bits of the CAS (Column Address Strobe) are modified internally to produce each address of the burst sequence” • BEDO memory speed ranged from 40-66 MHz which was faster than the FPM at 33MHz

BEDODRAM • At bus speeds at or below 100 MHz, BEDO would have been faster and more reliable than SDRAM • BEDO never really took off • There was more support for the production and development of SDRAM

SDRAM differs from past DRAM in two ways • The way it’s organized • Multiple banks on a single DIMM • Allows banks to recharge while others read/write • The way it’s controlled • Synchronous (aligned with the clock) • Performs commands that are fed by the clock signals

SDRAM Ratings • PC66, PC100, PC133 • SDRAM ratings which describe which bus speeds the RAM will support and work correctly with. • Ratings can also be in form x-y-z: • CAS latency (X) • RAS-to-CAS delay (Y) • RAS precharge time (Z) • There is tolerance • (83MHz,100MHz works in 66MHz bus)

RDRAM (Rambus) • Single chip • Low pin count • High capacity • High bandwidth

Double Data Rate SDRAMIntroduced in 2000 • - Doubles bandwidth by accessing data on both the “rising edge” and “falling edge” of the memory bus clock • - 2.5V versus 3.3V of the PC133 SDRAM • 184-pin DDR DIMMs versus 168-pin SDRAM DIMMs

DDR SDRAM Politics • ISSUE 1 – Support • AGP standard (NVIDIA GeForce 3D) • Intel exclusive deal with Rambus • AMD and VIA support DDR SDRAM

Micron Mitsubishi Toshiba NEC DDR SDRAM Manufacturers • Hitachi • Hyundai • IBM • Infineon

DDR SDRAM Politics • Issue 2 – Name • Proposed: • DDR SDRAM PC200/266 • (100/233 MHz memory bus) • Conflict: • Rambus RDRAM PC600/700/800

DDR SDRAM Politics • Issue 2 – Name (cont.) • DDR SDRAM Resolve… use the peak data transfer rate… • PC1600 = PC200 Formula (64 bit * 2 * 100MHz = 1600 MB/sec) • PC2100 = PC233 Formula (64 bit * 2 * 133MHz = 2133 MB/sec

Citations • Arnold, Eric (2002). “Computer Memory Ram Sdram Buffered Pc66 Pc100 Pc133 Mem Dram.” URL: http://home.cfl.rr.com/bjp/ • Cullen, Drew (2002). “Hynix Rations DDR Supply.” URL: http://www.theregister.co.uk/content/3/23876.html • Howe, Denis (1996). “Dynamic Random Access Memory by FOLDOC.” URL: http://wombat.doc.ic.ac.uk/foldoc/foldoc.cgi?DRAM • Howe, Denis (1996). “Page-Mode Dynamic Random Access Memory.” URL: • http://burks.brighton.ac.uk/burks/foldoc/94/85.htm • Kanellos, Michael (2002). “Memory Market Optimistic about 20002.” URL: http://zdnet.com.com/2100-1103-858175.html • Kozierok, Charles (2001). “PC-Guide Ref DRAM Technologies.” URL: http://www.pcguide.com/ref/ram/tech_FPM.htm

Citations • Kozierok, Charles (2001). “PC-Guide Ref DRAM Technologies.” URL: http://www.pcguide.com/ref/ram/techDDRSDRAM-c.html • Micron Technology(2000) “Memory Upgrades.” URL: http://www.crucial.com/DDR/index.asp • Pabst, Thomas (2002). Tom’s Hardware Guide, “RAM Guide.” URL: http://www6.tomshardware.com/mainboard/98q4/981024/ • Russell, Rick (2000). “The Memory Conundrum.” URL: • http://peripherals.about.com/library/weekly/aa021300a.htm?terms=DDR+DRAM • Thing, Lowell (2001). “What is.” URL: http://whatis.techtarget.com/definition/0,,sid9_gci213955,00.html