Fetch Execute Cycle

Fetch Execute Cycle. Travis Griffiths. Naming Conventions and Disclaimer. Individual registers in a particular CPU will have different names depending on the documentation used.

Fetch Execute Cycle

E N D

Presentation Transcript

Fetch Execute Cycle Travis Griffiths

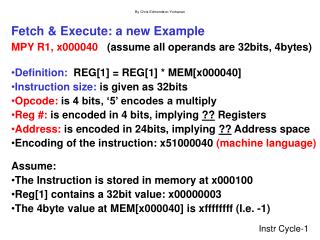

Naming Conventions and Disclaimer • Individual registers in a particular CPU will have different names depending on the documentation used. • Due to differences in design the exact specifics of any particular processor will be different, possibly even within the same processor Example: large addresses may require multiple passes to fully decode.

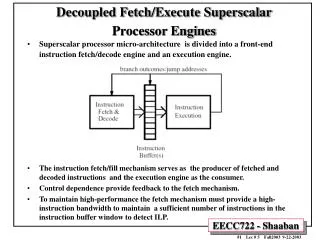

Steps of Fetch Execute Cycle • Fetch • The next instruction must be located, moved across at least one system bus to the processor • Execute • The instruction must be carried out, this often requires information be moved around in one or more registers and system memory.

Registers • Instruction Pointer (IP) • The location of the next instruction. • Sometimes called the Program Counter (PC) • Memory Access Register (MAR) • Current Instruction Register (CIR) or (IR) • The current instruction. • Accumulator (AX) • Used for short term storage, and in many instructions

Busses • Address Bus • Moves locations of data to different registers, particularly between the Instruction Pointer, Memory Address Register, and Memory • Data Bus • Moves contents of memory addresses

What is a Bus Anyway? Explicitly connecting every component in a system results in an exponential growth of connections. Bus interconnection solves this. A bus connection (n(n-1))/2 connections

Fetching an Instruction Memory location contents Instruction Pointer 0001 0001 0FFF 0002 0FA0 Address Bus 0003 010D 0004 00C1 0005 0010

Fetching an Instruction Memory location contents Instruction Pointer 0001 0001 0FFF 0002 0FA0 Address Bus 0003 010D Contents of the Program Counter are passed across the Address Bus 0004 00C1 0005 0010

Fetching an Instruction Memory location contents Instruction Pointer 0001 0001 0FFF The address moves over the address bus to the Memory Access Register 0002 0FA0 Address Bus 0003 010D 0001 0004 00C1 Memory Access Register 0005 0010

Fetching an Instruction Memory location contents 0001 0FFF The memory location of the next instruction is located. 0002 0FA0 0003 010D 0001 0004 00C1 Memory Access Register 0005 0010

Fetching an Instruction Memory location contents Data Bus 0001 0FFF The contents of memory at the given location are moved across the data bus 0002 0FA0 0003 010D 0004 00C1 0005 0010

Fetching an Instruction Memory location contents Data Bus 0001 0FFF 0002 0FA0 Into the instruction register (IR) 0003 010D 0FFF 0004 00C1 Instruction Register 0005 0010

Fetching an Instruction With the instruction loaded from memory into the Instruction Register the fetch portion of the cycle is complete. 0FFF Instruction Register

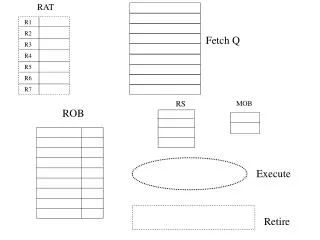

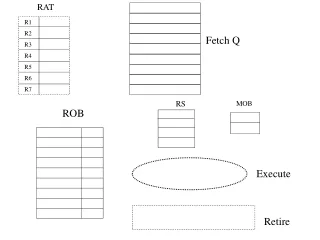

Notes on Fetch • This model assumes a simple fetch as our memory length all fits as a single unit in our registers. • Some processors make use of a queue to “preload” instructions. This speeds up execution as memory is slower than the CPU and many cycles are wasted waiting for instructions to arrive.

Execute The specifics of an Execute cycle are particular to the instruction that has just been loaded. Instruction sets are particular to a processor and will often make use of other registers within the system.