Finite State Machine Implementation (1)

Finite State Machine Implementation (1). Schematic and HDL Methods. Which Do You Use For FSMs?. Schematics HDL VHDL Verilog C++ Other HDL Combination 25% Schematic 50% Schematic 75% Schematic 100% Schematic. The Null Hypothesis:.

Finite State Machine Implementation (1)

E N D

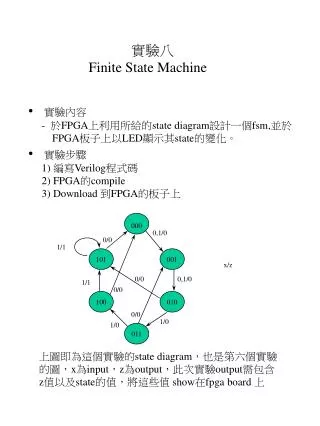

Presentation Transcript

Finite State Machine Implementation (1) Schematic and HDL Methods

Which Do You Use For FSMs? • Schematics • HDL • VHDL • Verilog • C++ • Other HDL • Combination • 25% Schematic • 50% Schematic • 75% Schematic • 100% Schematic

The Null Hypothesis: Coding in HDLs can often lead to unreviewable designs, failures, and be slower, worse, and more expensive than schematics.

“Coding Correctness” (CC)and HDLs • Can design larger circuits • Work at a higher level of abstraction • The synthesizer does all the hard work • The manufacturers will stop supporting schematic entry • It’s the “wave of the future”

The Alternate Hypothesis You guys are old and obsolete.

Notes from ReviewersExamples from Two Flight Projects I've been pondering VHDL coding styles lately, seeing as how I've been beating my head against the BOM FPGA for months now. The main part of the BOM is described in 33 pages of spaghetti VHDL that is broken into 5 processes, one of which is 16 pages long. There's no block diagram and very little descriptive text to guide one through the design. In contrast, the 29KPL154 [microcontroller] was easy to read because it started with a block diagram and treated each block as a component; I don't think many of the components were longer than 2 pages. I can see how VHDL could be made easier to read if some rules were enforced. The VHDL description started with 16 pages of structural VHDL with no comments. It was a mess and making a schematic from that, by hand, was painful. I never did finish the review as the design needed so many changes to make it flight worthy that it made more sense to simply trash it and start over. Modifying that mess would simply be too error prone.

“But that’s not me! No real engineer would do that. They’re just making that crap up!!!!!!”

A Flight VHDL Example (1) -- signal declarations --internal signal rst, cs, ale_n, pulse1_n, pulse2_n, gate, gate_del, int_tx_gate : std_logic; signal ck8hz, det_start_count, det_stop_count : std_logic; signal datout : std_logic_vector(7 downto 0); signal address : std_logic_vector(7 downto 0); signal dec_addr : std_logic_vector(5 downto 0); signal p1neg0, p1pos0, p2neg0, p2pos0 : std_logic_vector(19 downto 0); signal p1neg1, p1pos1, p2neg1, p2pos1 : std_logic_vector(19 downto 0); signal p1neg2, p1pos2, p2neg2, p2pos2 : std_logic_vector(19 downto 0); signal p1neg3, p1pos3, p2neg3, p2pos3 : std_logic_vector(19 downto 0); signal p1neg4, p1pos4, p2neg4, p2pos4 : std_logic_vector(19 downto 0); signal p1neg5, p1pos5, p2neg5, p2pos5 : std_logic_vector(19 downto 0); signal p1neg6, p1pos6, p2neg6, p2pos6 : std_logic_vector(19 downto 0); signal p1neg7, p1pos7, p2neg7, p2pos7 : std_logic_vector(19 downto 0); signal p1neg8, p1pos8, p2neg8, p2pos8 : std_logic_vector(19 downto 0); signal p1neg9, p1pos9, p2neg9, p2pos9 : std_logic_vector(19 downto 0); signal p1neg_tx, p1pos_tx : std_logic_vector(19 downto 0); signal count : std_logic_vector(22 downto 0); signal latch_count : std_logic_vector(15 downto 0); signal start_count, stop_count : std_logic_vector(21 downto 0); signal count_pulses : std_logic_vector(3 downto 0); signal reset_pulse_counter : std_logic; signal stop_gate, reset_gate_pulse : std_logic; constant count_to_8hz: integer := 7812499;

A Flight VHDL Example (2) begin -- Component instances power_on_reset : DEMETA port map(ck => clk62_5mhz, reset_in => pwronrst(0), rstout => rst ); counter_8hz : counter generic map ( num_bits => 23, last_count => count_to_8hz ) port map(reset => rst, ck => clk62_5mhz, enable => '1', count => count ); counter_pulses : counter generic map ( num_bits => 4, last_count => 9 ) port map(reset => reset_pulse_counter, ck => pulse2_n, enable => '1', count => count_pulses );

A Flight VHDL Example (3) ADDRESS_DECODER: decoder generic map ( innum_bits => 3, outnum_bits => 6 ) port map ( din => address(2 downto 0), enable => cs, dec_addr => dec_addr ); ADDRESS_LATCH : reg generic map ( num_bits => 8, reset_value => 255 ) port map(data => ad(7 downto 0), ck => ale_n, reset => pwronrst(0), ena => '1', q => address );

A Flight VHDL Example (4) START_GATE_21_16 : reg generic map ( num_bits => 6, reset_value => 63 ) port map(data => ad(5 downto 0), ck => wr_n, reset => pwronrst(0), ena => dec_addr(2), q => start_count(21 downto 16) ); STOP_GATE_7_0 : reg generic map ( num_bits => 8, reset_value => 250 ) port map(data => ad, ck => wr_n, reset => pwronrst(0), ena => dec_addr(3), q => stop_count(7 downto 0) ); START_GATE_7_0 : reg generic map ( num_bits => 8, reset_value => 255 ) port map(data => ad, ck => wr_n, reset => pwronrst(0), ena => dec_addr(0), q => start_count(7 downto 0) ); START_GATE_15_8 : reg generic map ( num_bits => 8, reset_value => 255 ) port map(data => ad, ck => wr_n, reset => pwronrst(0), ena => dec_addr(1), q => start_count(15 downto 8) );

A Flight VHDL Example (5) counter_pipeline : reg generic map ( num_bits => 16, reset_value => 0 ) port map(data => count(15 downto 0), ck => clk62_5mhz, reset => rst, ena => '1', q => latch_count ); PULSE1_NEG_LATCH0 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data(15 downto 0) => latch_count, data(19 downto 16) => ph, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg9 ); STOP_GATE_15_8 : reg generic map ( num_bits => 8, reset_value => 255 ) port map(data => ad, ck => wr_n, reset => pwronrst(0), ena => dec_addr(4), q => stop_count(15 downto 8) ); STOP_GATE_21_16 : reg generic map ( num_bits => 6, reset_value => 63 ) port map(data => ad(5 downto 0), ck => wr_n, reset => pwronrst(0), ena => dec_addr(5), q => stop_count(21 downto 16) );

A Flight VHDL Example (6) PULSE2_POS_LATCH0 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data(15 downto 0) => latch_count, data(19 downto 16) => ph, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos9 ); PULSE1_NEG_LATCH1 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg9, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg8 ); PULSE1_POS_LATCH0 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data(15 downto 0) => latch_count, data(19 downto 16) => ph, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos9 ); PULSE2_NEG_LATCH0 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data(15 downto 0) => latch_count, data(19 downto 16) => ph, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg9 );

A Flight VHDL Example (7) PULSE1_POS_LATCH1 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos9, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos8 ); PULSE2_NEG_LATCH1 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg9, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg8 ); PULSE2_POS_LATCH1 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos9, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos8 ); PULSE1_NEG_LATCH2 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg8, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg7 );

A Flight VHDL Example (8) PULSE1_POS_LATCH2 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos8, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos7 ); PULSE2_NEG_LATCH2 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg8, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg7 ); PULSE2_POS_LATCH2 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos8, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos7 ); PULSE1_NEG_LATCH3 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg7, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg6 );

A Flight VHDL Example (9) PULSE1_POS_LATCH3 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos7, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos6 ); PULSE2_NEG_LATCH3 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg7, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg6 );

A Flight VHDL Example (10) PULSE2_POS_LATCH3 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos7, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos6 ); PULSE1_NEG_LATCH4 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg6, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg5 ); PULSE1_POS_LATCH4 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos6, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos5 ); PULSE2_NEG_LATCH4 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg6, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg5 );

A Flight VHDL Example (11) PULSE2_POS_LATCH4 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos6, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos5 ); PULSE1_NEG_LATCH5 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg5, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg4 ); PULSE1_POS_LATCH5 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos5, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos4 ); PULSE2_NEG_LATCH5 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg5, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg4 );

A Flight VHDL Example (12) PULSE2_POS_LATCH5 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos5, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos4 ); PULSE1_NEG_LATCH6 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg4, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg3 ); PULSE1_POS_LATCH6 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos4, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos3 ); PULSE2_NEG_LATCH6 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg4, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg3 );

A Flight VHDL Example (13) PULSE2_POS_LATCH6 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos4, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos3 ); PULSE1_NEG_LATCH7 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg3, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg2 ); PULSE1_POS_LATCH7 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos3, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos2 ); PULSE2_NEG_LATCH7 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg3, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg2 );

A Flight VHDL Example (14) PULSE2_POS_LATCH7 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos3, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos2 ); PULSE1_NEG_LATCH8 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg2, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg1 ); PULSE1_POS_LATCH8 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos2, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos1 ); PULSE2_NEG_LATCH8 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg2, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg1 );

A Flight VHDL Example (15) PULSE2_POS_LATCH8 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos2, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos1 ); PULSE1_NEG_LATCH9 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1neg1, ck => pulse1_n, reset => pwronrst(1), ena => '1', q => p1neg0 ); PULSE1_POS_LATCH9 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p1pos1, ck => pulse1, reset => pwronrst(2), ena => '1', q => p1pos0 ); PULSE2_NEG_LATCH9 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2neg1, ck => pulse2_n, reset => pwronrst(3), ena => '1', q => p2neg0 );

A Flight VHDL Example (16) PULSE1_POS_LATCH_TX : reg --Tx Pulse positive edge generic map ( num_bits => 20, reset_value => 0 ) port map(data(15 downto 0) => latch_count, data(19 downto 16) => ph, ck => pulse1, reset => pwronrst(2), ena => int_tx_gate, q => p1pos_tx ); PULSE2_POS_LATCH9 : reg generic map ( num_bits => 20, reset_value => 0 ) port map(data => p2pos1, ck => pulse2, reset => pwronrst(4), ena => '1', q => p2pos0 ); PULSE1_NEG_LATCH_TX : reg --Tx Pulse positive edge generic map ( num_bits => 20, reset_value => 0 ) port map(data(15 downto 0) => latch_count, data(19 downto 16) => ph, ck => pulse1_n, reset => pwronrst(1), ena => int_tx_gate, q => p1neg_tx );

“Computer Science World Mourning the Loss of Two of Its Trailblazers” Dijkstra opposed the GOTO statement and worked to abolish it from programming. In a March 1968 letter to the editor of Communications of the ACM, he contended that the more GOTO statements there are in a program, the harder it is to follow the source code. The letter is acknowledged to have initiated the movement to produce reliable software by developing structured programs. EE Times, August 26, 2002, p. 20

Discussion: What is the difference between a GOTO statement and structural VHDL? Why has the GOTO statement been considered EVIL by Computer Scientists for 40 years but is now present in HDL-based hardware designs?