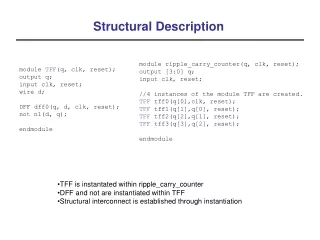

Structural Description

Structural Description. Components and their instantiation Configuration Components in package. Example for Structural Description. Entity mux is port (d0,d1,sel: in std_logic; q: out std_logic); end; Architecture str of mux is -- Component declaration

Structural Description

E N D

Presentation Transcript

Structural Description Components and their instantiation Configuration Components in package

Example for Structural Description Entity mux is port (d0,d1,sel: in std_logic; q: out std_logic); end; Architecture str of mux is -- Component declaration component and_comp port (a,b: in std_logic; c: out std_logic); end component; component or_comp port (a,b: in std_logic; c: out std_logic); end component; component inv_comp port (a: in std_logic; b: out std_logic); end component; signal i1,i2,sel_n:std_logic; -- Component specification for U1: inv_comp Use Entity work.inv_comp(rtl); for U2,U3: and_comp Use Entity work.and_comp(rtl); for U4: or_comp Use Entity work.or_comp(rtl);

Example for Structural Description (cont.) begin -- Component instantiation U1: inv_comp port map(sel,sel_n); U2: and_comp port map(d0,sel,i1); U3: and_comp port map(sel_n,d1,i2); U4: or_comp port map(i1,i2,q); end;

Component Declaration • For a VHDL component to be instanced with structural VHDL, it first has to be declared • This is done in the concurrent declaration part of the architecture • Syntax: component <entity_name> [generic(<generic-association-list>);] port(<port-association-list>); end component; • Port_list in the component declaration must be identical to that in the component’s entity • The best way of guaranteeing this is to copy the entity to the component declaration or vice versa • Generic parameters do not need to be declared in the component declaration

Component Instantiation • component_instantiation_statement ::=instantiation _label : instantiated_unit [ generic_map_aspect ] [ port_map_aspect ] ; • Example: • u_myent: ENTITY work.my_entity(bhv)PORT MAP (I1 => S1 , I2 => S2 ) ; • The entity my_entity is directly instantiated • The signals I1 and I2 of my_entity are connectedwith the local signals S1 and S2

A NAND component entity nand_comp is port( a,b: in std_logic; c: out std_logic); end; architecture nand_bhv of nand_comp is signal int: std_logic; -- Internal signal declaration begin int <= a and b; c <= not int; end;

Component instantiation U1: nand_comp port map (a => wire1, b => wire2, c => wire3); • The component nand_comp is instanced and given the name U1 • Each name of a new instance of nand_comp must be an unique name

Configuration I • A configuration binds an architecture to an entity • In a lot of CAE tools there is not configuration at all or the integrated tool has configuration functionality • In the next example the configuration is described in VHDL language • The entity mux has two different architectures, the rtl and bhv • The configuration specifies, which is to be simulated • The name of the configuration which results in the rtl architecture being simulated is mux_rtl • while that for the bhv architecture is mux_bhv entity mux is port(a,b,c,d: in std_logic_vector(3 downto 0); sel :in std_logic_vector(1 downto 0); q : in std_logic_vector(1 downto 0)); end;

Configuration II architecture bhv of mux is begin process(a,b,c,d,sel) variable int: std_logic_vector(3 downto 0); begin case sel is when “00” => int<=a; when “01” => int<=b; when “10” => int<=c; when “11” => int<=d; whenothers => int<=(others =>‘X’); end case; q<=int after 10 ns; end process; end;

Configuration III architecture rtl of mux is begin process(a,b,c,d,sel) begin case sel is when “00” => q<=a; when “01” => q<=b; when “10” => q<=c; whenothers => q<=d; end case; end process; end;

Configuration IV -- Configuration for architecture bhv configuration bhv of mux is for bhv end for; end bhv; -- Configuration for architecture rtl configuration rtl of mux is for rtl end for; end rtl; • Depending on which of the configurations is compiled, architecture bhv or rtl will be simulated • The component specification is a simplified form of the configuration • The component specification is placed in hte declaration part of the architecture for the component to be simulated • The configuration is mainly used in design of simulatable models, in case of hardware design the tools avoid it

Direct Instantiation • Direct instantiation of components is introduced in the VHDL-93 standard • It means that neither component declaration nor configuration are needed to instance a component • The next example shows the difference between the two instantiation method: -- Model according to VHDL-87 architecture rtl of top_level is component c1 port(a,b: in std:logic; q: out std_logic); end component; for U1: c1 use entity work.c1(rtl); begin U1: c1 port map(a,b,q); end; -- Model according to VHDL-93 architecture rtl of top_level is begin U1: entity work.c1(rtl) port map(a,b,q); end;

Components in packages I • If the components are defined in packages, no component declaration is needed in the architecture when the component is instantiated • Example: package mypack is function minimum (a,b:in std_logic_vector) return std_logic_vector; component c1 port(clk,resetn,din:in std_logic; q1,q2:out std_logic); endcomponent; component c2 port(a,b:in std_logic; q:out std_logic); endcomponent; end mypack; package body mypack is function minimum (a,b:in std_logic_vector) return std_logic_vector is begin if a<b then return a; else return b; end if; end minimum; end mypack;

Components in packages II • To use the component the declaration of the package is needed in the beginning of the VHDL code, only: library ieee; use ieee.std_logic_1164.ALL; use work.mypack.ALL; entity ex is port(clk,resetn:in std_logic; d1,d2:out std_logic; a,b: in std_logic_vector(3 downto 0); q1,q2,q3: out std_logic; q4:out std_logic_vector(3 downto 0)); end; Architecture rtl of ex is begin U1: c1 port map(clk,resetn,d1,q1,q2); U2: c2 port map(d1,d2,q3); q4<=minimum(a,b); end;

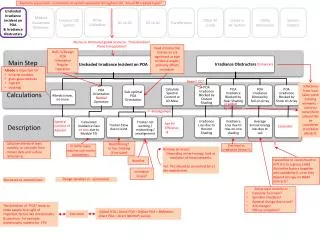

Formal Checkers (FoCs) • A productivity tool for automatic generation of simulation monitors from formal specifications • It greatly aids chip designers and verification engineers in the complex, costly task of verifying chip designs before submitting them to manufacturing • FoCs users report a drastic improvement (up to 50%) in "testbench" development time • FoCs takes properties written in a special specification language and automatically translates them into Checkers, which in turn are integrated into the chip simulation environment • These Checkers monitor the simulation results on a cycle-by-cycle basis for violation of the properties • Each Checker implements a state machine that enters and asserts an error stateif the respective property fails to hold in a simulation run • FoCs can also be used for coverage analysis, that is, to create checkers that track the occurrences of events of interest during simulation • FoCs can produce code in VHDL, and it supports the conventions of popular simulators such as Model Technology's ModelSim